#### A Content Addressable Parallel Array Processor

Caxton Foster Charles Weems Steven Levitan

COINS Technical Report 83-32

Department of Computer and Information Science

University of Massachusetts

Amherst, Massachusetts, 01003

September 1983

# Table of Contents

| Features of Titanic                                                                                                         | 1  |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Titanic: A VLSI Based Content Addressable Parallel Array Processor                                                          | 7  |

| An Algorithm for a Simple Image Convolution on the<br>Titanic Content Addressable Parallel Array Processor                  | 33 |

| Finding a Center of Mass with a CAM                                                                                         | 44 |

| Determination of the Rotational and Translational Components of a Flow Field Using a Content Addressable Parallel Processor | 53 |

| Extract from: Incorporating Content Addressable Array Processors into Computer Vision Systems                               | 58 |

| Real Time LISP Using Content Addressable Memory                                                                             | 62 |

| Decryption of Simple Substitution Cyphers with Word Divisions Using a Content Addressable Memory                            | 71 |

The papers contained in this collection were funded by a variety of granting agencies and sources. These are individually acknowledged in each of the papers.

:

# A Content Addressable Parallel Array Processor

The Titanic Parallel Array Processor is a Single Instruction Stream Multiple Data Stream (SIMD) machine which will be connected, as a slave device, to a VAX-11/780. Like the Floating Point Systems AP120B slave processor, it can be used for vector processing, but it is actually a general purpose parallel processor like the Illiac IV or Staran. The Titanic will be used both as a research project for the investigation of parallel processing systems and as a tool for other researchers who are investigating such computationaly intensive applications as static image processing, motion image processing, robotics, and neural-network algorithms.

The Titanic general purpose parallel processor is necessary because there are many problems which are so computationally intensive that even the fastest general purpose serial processors are unable to solve them in real time, for example, real time signal processing, computer vision, speech understanding and robot sensory analysis. Although special purpose machines exist to solve some of these problems in a limited domain, they do not provide the flexibility necessary to allow the exploration of new solutions to the problems or adaptation to new domains. The Titanic will provide this flexibility as well as the raw computing power necessary to solve these problems.

There are many problems which are still compute-bound, even in this era of Cray 2s and Floating Point Systems vector processors. Examples of such problems include image processing, motion analysis searching, sorting, pattern recognition, database management, etc. Speaking generally, the availability of a CAM enables one to approach the solution of a problem in ways that would be rejected out-of-hand in a von-Neumann organization. Below are some examples of the kinds of problems and solutions we have worked on to date.

- \* Storing and searching a dictionary of several thousand common English words, Wall found that the CDC-6600 might take up to several hours to solve a single simple substitution cryptogram. The same approach implemented on a CAM could solve the same cryptogram in approximately half a second. Suddenly, an "obvious" approach that had been completely impractical becomes very attractive.

- \* In a data base application, storing key descriptive words in the CAM, we can let a user enter information in very nearly normal English, pick out the key words he uses, and do an incremental search while he is still inputting his description or query.

- \* One of the problems that inhibits the use of LISP for real-time applications is due to the unpredictable and arbitrarily long delays that occur when main memory becomes full and garbage collection must be performed.

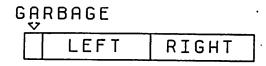

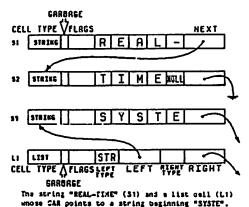

A typical LISP cell in a CAM might contain three fields (at least) called "garbage" (one bit long), "left" (CAR), and "right" (CDR). When a free cell is needed, we search for a cell whose garbage bit is "1". Before we can use this cell, we must discover if it is the only cell in memory now pointing to the cell named in the "left" field (call it TARGET). In a CAM we can ask, in parallel, if there exist any cells

which point to TARGET in either their CAR or CDR. If there are none, then TARGET is also a garbage cell, and we set its garbage bit. A similar search must be done for the cell pointed at by the "right" field. Once these four searches have been done, and garbage bits set if required, the original cell can be reused. This takes only four exact match searches. Thus, LISP becomes available for real-time use where arbitrary delays might be fatal.

- \* Local, window-type convolutions are very common in signal processing and image processing applications, as well as many other areas. Indeed, much of the interest in Fast Fourier Transforms is because once the transform has been carried out, a simple multiplication followed by an inverse transform can be used to perform a convolution. In a CAM we can perform a simple convolution in about one hundred microseconds directly on the image in question without having to perform the transform and its inverse. The is some times faster than is possible on, for example, a Floating Point Systems AP120B vector processor.

- \* In the analysis of images taken by a moving camera one tries to identify "interesting points". Successive positions of an "interesting" point establish a "flow-vector" for that point and a set of such flow-vectors, when projected, can be used to identify the FOE (focus of expansion) which is the point toward which the camera is moving. Due to noise in the images and inherent digitization noise, the set of flow-vectors will not all intersect at a single point. Taken pairwise, the flow-vectors will intersect in a set of points and the center of mass of these intersection points is a good estimate of the FOE. Such a center of mass can be found in a CAM in under a millisecond, or roughly 1,400 times faster than a conventional machine.

Besides our own research groups at the University of Massachusetts, groups at Digital Equipment Corporation and General Electric Corporation have shown interest in the research. These companies are both investigating computer designs which solve computationally intensive problems such as signal processing, machine vision and robot control.

Once the Titanic actually exists, even more progress will be made by researchers who have access to it. These people are committed to spending the time and energy necessary to develop new algorithms, new theories, and new applications which take advantage of the advanced architecture and processing power of Titanic.

#### Things that Titanic is good at

- \* Anything that an associative processor like STARAN is good at:

- Database query/update

- Text to speech synthesis

- Real time LISP garbage collection

- Radar analysis

- Graph processing

- Digital differential analysis

- Air traffic control

- Scalar arithmetic (scalar \* vector)

- Vector arithmetic (vector \* vector)

- \* Anything that an SIMD parallel processing array like ILLIAC IV is good at:

- Convolution

- Relaxation

- Simulation of planar dynamic physical systems (fluidics, weather, crystal lattices)

- Modelling

- Signal processing

- Edge detection

- Line thinning

- Image processing

- \* Things that neither of the above architectures is good at but which the combination can do:

- Segmentation

- Converting a segmented image into a graph representation

- Region specific adaptive image enhancement

- Histogram analysis

- Some forms of Hough transform

- Hidden line/surface removal

- Flow field determination from image sequences

- Stereo image correlation / depth extraction

#### Things Titanic is bad at

- \* Anything that only an MIMD architecture is good at.

- \* Some things that a shuffle-exchange network is good at.

- \* Examples:

- Distributed processing applications

- Matrix multiply

- Fast Fourier Transform

- Anything which requires complex or random parallel communication between distant nodes in a network.

Note: Titanic gets around the inability to do Matrix Multiply and FFT by doing directly many of the operations that these are needed for in other architectures. For example, FFT's are commonly used to do convolutions in image and signal processing. Titanic simply does the convolve directly, avoiding the FFT altogether, which results in a substantial speed increase.

#### Titanic:

A VLSI Based Content Addressable Parallel Array Processor\*

by

C. Weems

S. Levitan

C. Foster

Department of Computer and Information Science University of Massachusetts Amherst, Massachusetts 01003

#### Abstract

A design is presented for a Content Addressable Parallel Array Processor (CAPAP) which is both practical and feasible. Its practicality stems from an extensive program of research into real applications of content addressability and parallelism. The feasibility of the design stems from development under a set of conservative engineering constraints tied to limitations of VLSI technology.

A shortened version of this paper appeared in the proceedings of the 1982 International Conference on Circuits and Computers (September 29 to October 1, 1982, New York)

<sup>\*</sup>This work was supported in part by a grant from the Army Research Office DAAG29-79-G-0046.

#### <u>Origins</u>

Starting in the Summer of 1979, after acquiring a small Content Addressable Memory (CAM), we conducted an extensive exploration of applications of content addressability and parallelism. During the ensuing three years some thirty applications have been developed with over a dozen being programmed to completion. All have been analyzed with an eye toward the design of more useful hardware. Application areas have included data base retrieval, LISP garbage collection, text-to-speech synthesis, and image convolution. Some of the results of this work are presented here as a rationale for some of our architectural design decisions.

## More Cells With Less Memory

One of our major findings is somewhat counterintuitive. Normally, CAM designers give a large amount of memory to each cell of the CAM. This is so that each cell may hold a large record of logically associated data. Such a design maximize the benefits CAM's attempts to ofthe associativity. We have found, however, that a majority of interesting CAM applications require only one to sixteen bytes of memory in each cell, and that these applications benefit much more from the added parallelism of having more cells. Further, we have found that those applications which require more memory in each cell will work adequately if efficient means of moving data between cells is provided. Thus, we conclude that the resources required to construct large cell memories would be far better spent

constructing more cells with less memory.

### Need Fast Some/None and Find First

A common means of controlling loop execution in CAM algorithms is to continue processing until none or only one of the CAM's tag bits are turned on. It is thus essential that we have a fast means of determining this. The simplest way of doing this is to test whether any tags are on; if so, then we select one and turn it off, then repeat the some/none test. The find first operation is also used frequently when a search finds several data elements with the same key value. It then provides a way to select one of these for processing. These cases combine to emphasize the need for fast some/none and find first operations.

# Slower Response Count is Acceptable

Many CAM designs devote much complex and expensive hardware to increasing the speed of the operation which counts the tag bits that are turned on. We have found. however, that the count of responding tags is used primarily as a way of gathering statistics for use at much higher of processing control to direct the strategic levels application of the CAM. It is thus rather infrequently applied as compared to operations such as comparisons and some/none tests. We thus feel that slower, simpler, less expensive response count hardware is quite acceptable. Further, we have designed a very simple response count system which runs only about an order of magnitude slower than much more complex designs.

# Convenient Additions

CAMs typically have only one tag bit per cell. We have found, however, that most algorithms need two to four tags. Usually this is simulated by storing tag bits in the memory, however this becomes a major inconvenience when the cells have small memories. It is thus convenient to have multiple tag bits in each cell. Although any CAM with bit select and multi-write can perform bit-serial addition incidentally, is thus called a Content Addressable Parallel Processor -- CAPP -- see Foster [1]), it is far more convenient and several times faster to perform additions if each cell contains a full adder. Finally, we have also found it quite convenient if each cell is provided with a way of logically combining stored tag bits. When a CAPP is provided with these capabilities at the individual cell level, the result is a Single Instruction Multiple Data (SIMD) parallel processor of considerable power.

# An Image Processing CAPP

By the Winter of 1981 we had begun to examine application of a CAPP to image processing. We soon found that we were dealing with two kinds of problem solutions. One kind worked independently of where pixel values were placed in the CAPP. An example of this truly associative type of solution is histogram directed feature extraction. The other kind required that pixel data be combined and it

was thus necessary to use inter-cell communication links to accomplish this. Although we had already considered a linear cell interconnect (as a way to simulate cells with larger memories), we were now faced with problems that required a rectangular interconnect (hexagonal triangular interconnects were not considered digitized images do not map well onto them). An example of this is contrast enhancing image convolution. We also discovered that the edges of an image require special processing. Our solution to this problem was to provide a four-way (N, S, E, W,) cell inerconnect network with three different edge treatments. The simplest edge treatment dead-edging, that is making the edges of the grid act like a frame ofinactive cells. Another treatment is circular-wrap. In this case each edge cell is logically connected back around to its counterpart on the opposite The most complex treatment is zig-zag wrap in which edge. each edge cell is logically connected to a cell on the opposite edge that is offset by one row or column. last treatment provides a way to turn an essentially rectangular CAPP into a linear structure and thus make it more general.

Some practical aspects of designing an image processing CAPP include the need to be able to load the memory with an image in one video frametime (1/30 second). This may seem like a long time, but remember that a 512x512 image contains 262,144 pixels. For sixteen-bit pixels this means a data transfer rate of about sixteen million bytes per second. We

have also considered types of secondary storage that will be needed to keep up with such transfer rates. Hardware testing and debugging have also been major concerns simply because of the large number of components involved.

#### Titanic

In the Summer of 1981 we started work on the design of a VLSI-based CAPP for image processing. Our intent was to produce a conservative design which would be simple enough for us to construct with reasonable confidence of success but which would also provide a significant advance in processing power. From the beginning we imposed a number of constraints on the design. For example, the CAPP would have to consist of no more than one hundred circuit boards and each board should have a maximum of one hundred off-board connections. As another example, the VLSI chips we designed would be restricted to no more that 40,000 devices, have a pin-out of no more than forty pins, and dissipate less that two watts.

We also set a number of goals which we hoped to achieve. It was decided that the CAPP should contain 262,144 cells arranged as a rectangular 512x512 array to facilitate image processing. Each cell would contain at least thirty-two bits of memory, multiple tags, and some bit serial processing power. One hundred nanoseconds was set as a goal for the minor clock cycle time. We also planned to meet as many of the design recommendations established by our CAM research as we could. Finally, it was decided that

the CAPP would be built to be driven by another machine, such as a Digital Equipment Corporation VAX. Once the goals and constraints were set, work on the design got under way and, for obscure reasons, the project was given the name "Titanic".

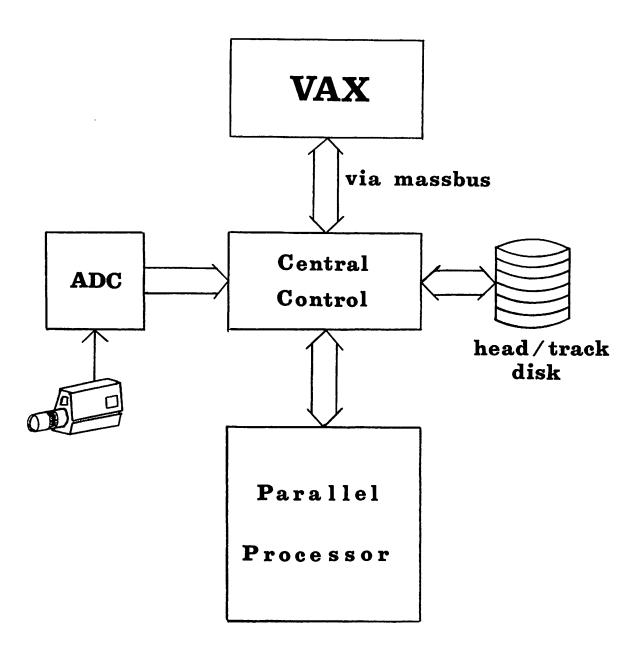

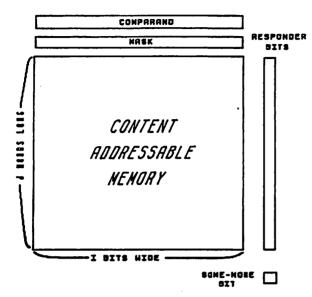

# Titanic and Its Environment

The Titanic is divided into two main parts: central control and the parallel processor. The central control is a simple, fast, fetch-ahead pipelined processor which will be built from MSI devices. It. instructions to the parallel processor, controls loading and unloading of data in the parallel processor, serves as an interface to the VAX or other host computer and to other data sources and secondary storage devices. The central controller contains a ROM with a set of micro-coded subroutines for performing commonly needed higher level CAPP operations, and a writeable control store which allows users to add their own special microcoded instructions. Also contained in the central controller is a small program memory into which subroutines or entire programs may be loaded. The writeable control store and program memory are loaded directly by the VAX. Once these memories are loaded, the VAX can issue commands to the central controller which tell it to execute routines stored in the program memory, to single step through a stored routine, or to execute a single instruction passed as a literal by the VAX. Figure 1 shows Titanic and its environment.

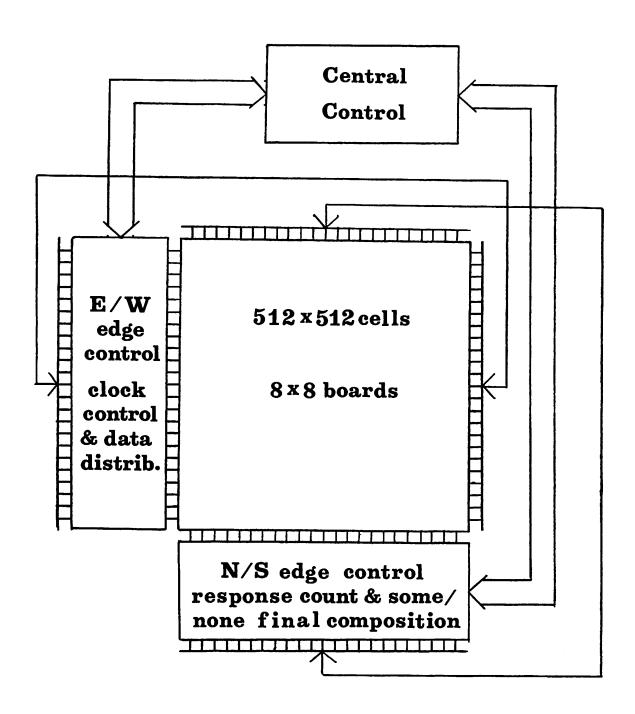

### The Parallel Processor

The Titanic parallel processor consists of an 8x8 array of processing circuit boards and a set of special purpose boards which control how the edges of the CAPP are treated, buffer broadcast signals, and perform other functions such as collecting the some/none signals to a single line. The parallel processor receives data and instructions broadcast to it by the central controller. Each parallel processor instruction operates in exactly one minor cycle time. Some operations do require multiple clock cycles, but these are taken care of by having the central control rebroadcast the instruction as many times as necessary. Figure 2 shows the structure of the parallel processor.

Each processor board consists of an 8x8 array of special CAPP integrated circuits plus some random buffer logic. A list of the sixty-three I/O lines on each board is given in Table 1. Our current design calls for all sixty-four processor circuit boards to be placed in four card racks (sixteen per rack) and interconnected by a broadcast backplane and ribbon cables.

# The Titanic IC

The heart of the Titanic design is a special purpose nMOS VLSI CAPP integrated circuit. Each of these chips contains sixty-four CAPP cells, an instruction decoder, and other miscellaneous logic. The design of this IC is actually much further along than the rest of the project (this being mainly due to test chip fabrication time

constraints). To compensate for this somewhat bottom-up development we have designed the chip with as much generality as possible, knowing that such generality need not be fully used later on.

### The Communications Interconnect

One of our biggest problems in designing Titanic was how to handle the rectangular interconnection of the cells. The number of wires required for such a network, even for bit serial communications, is staggering. This became most evident when we tried to design the IC communications interface. For sixty-four cells, the arrangement which gives the minimum number of external connections is an 8x8 grid. With a four-way N,S,E,W interconnect there are then only thirty-two neighboring cells to connect to. considered an eight-way N,S,E,W,NW,NE,SW,SE interconnect, but were forced to abandon it due to the wiring complexity.) By the time control, power, and clock signals were added to the thirty-two neighbor lines, we found that a sixty-four pin package would be required to hold the IC. Further examination also revealed that a full interconnect would require that each processor board have 256 ribbon cable communication lines -- in other words, a two foot wide swath of ribbon cable running between each pair of boards! Because this violated two of our main design constraints, we had to simplify the interconnect.

By 8:1 multiplexing the communications net as it crossed chip boundaries, we were able to reduce the IC pin count to twenty-two pins and the total board wire count to sixty-three (of which only thirty-two need to be run in ribbon cable). By going from sixty-four pin to twenty-two pin packages, the board size was also reduced significantly. Unfortunately, all of these benefits were paid for in a loss of speed. The new interconnect takes 0.8 microseconds to transfer one bit between cells (25.6 microseconds for thirty-two bits). We should also note here that the Titanic instruction set makes this multiplexing transparent to the user.

# Some/None Logic

On-chip the Some/None signal is determined by feeding the output of the main tag bit into a sixty-four-way NOR with an inverter between its output and the Some/None pad driver. Once the signal goes off-chip, it passes through a four-level OR tree before reaching the central controller.

# Count Responders

The count responders operation requires only three changes to be made to the CAPP circuitry to be feasible. Firstly, it must be possible to connect all of the response bits into a circular shift register. This is easily accomplished because the neighbor communication network already provides most of the necessary links. Secondly, a register, a counter, and a full adder must be added to each

chip. Finally, the cards that control the top-bottom edge treatment must be modified to include column summing registers and a final sum register.

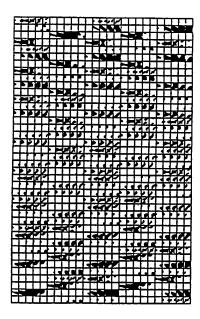

The algorithm used to count responders is given in Figure 3. This method is reasonably fast (about twenty-six microseconds), inexpensive, and most importantly it can be used with any size of array without having to modify the IC -- only the bottom row circuit board needs to be changed.

### Device Floorplan

Figure 4 shows the Titanic IC's floorplan. unit cells are arranged in two columns of thirty-two. arrangement was chosen because we found that the best compaction would be obtained if we could share control and memory select lines among as many cells as possible. Each cell is thus very long and narrow. A column of thirty-two cells is almost covered by a river of metal control select lines which run vertically over it. These lines are simply duplicated and mirrored for the two columns. Control is generated by a NOR-NOR network forming the instruction and address decoders. Responder count hardware is provided in a small block of random logic. The overall size estimate of the active chip area (excluding pads and drivers) 2400x2400 lambda. Thus if lambda is three microns, the central portion of the die would be roughly 285 mils on a This is somewhat large, but not unreasonable. side. dissipation is estimated at 1.5 watts, which is low enough to allow forced-air cooling. Table 2 lists the pin functions of the Titanic IC.

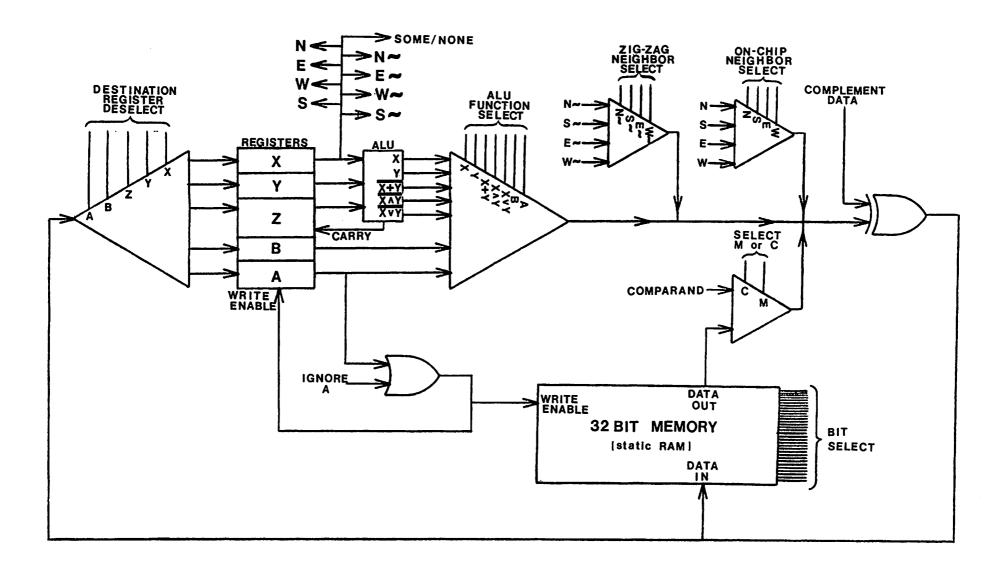

### The Unit Cells

A unit cell consists of thirty-two bits of fully static memory, four one-bit static tag "registers" called A, B, X, and Y, and a static carry bit "register" called Z. Each cell also contains an ALU which continuously generates X nand Y, X nor Y, and X + Y + Z. Finally, each cell contains logic for selecting some source of data (a register, memory, an ALU function, broadcast data, or a neighbor cell), possibly inverting the selected signal and storing it in a destination (memory or register). Neighbor communiation lines run vertically in two channels in the middle of the cell. The Z register is special in that it is not available for selection as a data source. It can be copied directly to the X register and can be loaded from the output of the selector. It also is loaded with the carry from X + Y + Z whenever that function is selected.

The X register is special in that its output is connected to the some/none logic and the neighbor communication network. In some sense it is the "main" tag bit.

The A register is also special. It controls whether the cell is active. If a cell is not active, it ignores all instructions broadcast by the central controller except a special few.

The Y register is intended to be used for storing a second set of tag bits which may eventually be combined with other sets through the logical operations provided by the ALU.

The B register is intended as temporary storage for a second set of activity bits, essentially providing a single level of "subroutine call" or an alternative activity "screen".

Figure 5 shows the logical arrangement of a unit cell while Figure 6 shows its silicon floorplan.

# Titanic IC Instruction Set

Table 3 lists the instruction set of the Titanic IC. Each instruction executes in one minor clock cycle (100 ns). This was done to avoid feedback loops in the decoder on the chip and to avoid special instruction states in the central controller. This means that the central controller must be programmed to re-issue some instructions several times. For example, transferring data to neighbor cells across chip boundaries requires eight individual transfers because of the 8:1 multiplex. The central control must therefore issue the shift instruction eight times in a row. This, of course, will be encoded as a single operation in the controller's microcode ROM.

There are eight basic instructions recognized by the chip. Of these, six are memory transfer operations and use a five-bit address value to select the bit to be read or written. The other two instructions treat the address as a

sub-operation specifier. For the most part these are non-memory data source to register data transfer operations with one op code causing the data to be inverted before storage and the other causing a direct transfer. There are nineteen special sub-ops, however, which are reserved for unusual operations such as transferring data on and off the chip or counting responders.

Some operations (those followed by exclamation points (!) in Table 3) are also designated as "jam transfers". This means that they are performed regardless of whether the A register contains a logic one. These provide a means of storing and retrieving different activity patterns and of applying global operations which ignore activity without the usual overhead of having to save the current activity pattern, and retrieve it later.

#### Current Status

As of this writing we have designed a sixteen-cell (4x4) test chip, and are negotiating for fabrication. Using a simple set of three micron design rules, we have succeeded in fitting the circuitry onto a 180x180 mil body area with room to spare. The actual cell area occupies only 130x106 mils. Estimated power dissipation is only 350 milliwatts. The design includes about 7000 transistors.

We have already written a number of programs for the Titanic and estimated their operation times by hand. For example, one special purpose convolution of interest in computer vision processing (a simple 3x3 mask) required only

97.8 microseconds for the entire 512x512 image. More complex convolutions take longer, of course, but most of interest can be performed in less than five milliseconds. We have also examined motion analysis and found the results to be quite encouraging.

#### Further Research

Based on the results of our test chip experience, we intend to proceed to full sixty-four cell ICs and, eventually, construction of the entire machine. Architectural changes which we intend to pursue are increasing the memory size to sixty-four bits per cell and perhaps going to an 8:2 communications multiplex (with a twenty-eight pin package) for a doubling in the data transfer rate.

We also plan to program a statistics gathering Titanic simulator which will allow us to experiment with software development and optimization.

Our work thus far has indicated that a Content Addressable Parallel Array Processor is extremely well suited for image processing, vision, and motion analysis. We intend to pursue further applications in these areas and also in new areas such as tactile object recognition in robotics.

# Conclusion

Rationale and a design have been presented for a Content Addressable Parallel Processor suitable for both general use and image processing applications. The architecture of the processor is based in practical experience and the hardware design has been constrained to make it possible to construct using existing technology and with a high confidence of success. Despite these constraints, simulations have shown that such a machine would provide a significant increase in processing power over what is presently available.

#### References

[1] Foster, Caxton C., <u>Content</u> <u>Addressable</u> <u>Parallel</u> <u>Processors</u>, Van Nostrand Reinhold, New York, 1976.

# <u>List of Processor Board I/O Lines</u>

| Number of Lines                                          | <u>Function</u>                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8<br>8<br>8<br>8<br>8<br>4<br>5<br>1<br>1<br>2<br>1<br>1 | Bidirectional North Neighbor Communications Bidirectional South Neighbor Communications Bidirectional East Neighbor Communications Bidirectional West Neighbor Communications Chip Column Select Chip Row Select Op Code Bit Address or Sub Op Code Broadcast Comparand Data Some/None Output Clock phases Power Ground |

Table 1

# <u>List of Titanic IC Pin Assignments</u>

| <u>Pin</u>                      | <u>Function</u>                                               |

|---------------------------------|---------------------------------------------------------------|

| 1<br>2                          | West Neighbor Communications (Bidirectional)<br>Chip Select 1 |

| 3<br>4<br>5<br>6<br>7<br>8<br>9 | South Neighbor Communications (Bidirectional) Op Code Bit 1   |

| 5<br>6                          | Op Code Bit 2<br>Op Code Bit 3                                |

| 7                               | Op Code Bit 4<br>Comparand in                                 |

|                                 | Some/None out                                                 |

| 10<br>11                        | Clock Phase 1<br>Ground                                       |

| 12                              | East Neighbor Communications (Bidirectional)                  |

| 13<br>14                        | Chip Select 2<br>Spare (Test)                                 |

| 15                              | Address Bit 5                                                 |

| 16<br>17                        | Address Bit 4                                                 |

| 17<br>18                        | Address Bit 3<br>Address Bit 2                                |

| 19                              | Address Bit 1                                                 |

| 20<br>21                        | North Neighbor Communications (Bidirectional) Clock Phase 2   |

| 22                              | Power                                                         |

Table 2

Titanic IC Instruction Set

| Memory         | Operati |          | CODE R/W ADDRESS                |

|----------------|---------|----------|---------------------------------|

| <u>0p</u><br>0 | R/W     | FUNCTION | ! - Transfer ignores activity   |

|                | 0       | M:=C     | A - Activity register           |

| 0              | 1       | A:=M     | B - Secondary Activity register |

| 1              | 0       | M:=B     | C - Comparand                   |

| 1              | 1       | B:=M     | M - Memory                      |

| 2              | 0       | M:=X     | X - Main tag register           |

| 2              | 1       | X:=M     | Y - Secondary tag register      |

| 3              | 0       | M:=Y     | Z - Carry register              |

| 3<br>3<br>4    | 1       | Y:=M     | N - Data from North             |

| 4              | 0       | M:=A!    | E - Data from East              |

| 4              | 1       | A:=M!    | W - Data from West              |

| 5              | 0       | M:=B!    | S - Data from South             |

| 5              | 1       | B:=M!    |                                 |

| Register Op                          | erations | OP-CODE DEST                                  |                                               | OP CODE 6 - NORMAL OP CODE 7 - INVERT SOURCE |

|--------------------------------------|----------|-----------------------------------------------|-----------------------------------------------|----------------------------------------------|

|                                      |          | Destinatio                                    | on                                            |                                              |

| Source                               | 0        | 1 1                                           | 2                                             | 3                                            |

| 0                                    | X := A ! | A:=B                                          | B:=A!                                         | Y:=A!                                        |

| 1                                    | X:=B     | A:=B                                          | B:=B                                          | Y:=B                                         |

| 2                                    | X:=X     | A:=X                                          | B:=X                                          | Y:=X                                         |

| 3                                    | X:=Y     | A: <u>=Y</u>                                  | B: <u>=Y</u>                                  | Y:=Y                                         |

| 4                                    | X:=X+Y   | $A:=X+\overline{Y}$                           | $B:=\overline{X+Y}$                           | $Y := \overline{X + Y}$                      |

| 5                                    | X:=X^Y   | $A := X^{A}Y$                                 | B := X Y                                      | $Y := X^{-}Y$                                |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | X:=XvY   | $A := \overline{X} \overline{V} \overline{Y}$ | $B := \overline{X} \overline{V} \overline{Y}$ | $Y := \overline{X} \overline{Y}$             |

| 7                                    | X:=C     | A:=C                                          | B:=C                                          | Y:=C                                         |

| 8                                    | X:=N     | A:=N                                          | B:=N                                          | Y:=N                                         |

| 9                                    | X:=E     | A:=E                                          | B:=E                                          | Y:=E                                         |

|                                      | X:=W     | A:=W                                          | B:=W                                          | Y:=W'                                        |

| 11                                   | X:=S     | A:=S                                          | B:=S                                          | Y:=S                                         |

| 12                                   | X:=N~!   | A:=C!                                         | X:=CN~!                                       | Z:=C                                         |

| 13                                   | X:=E~!   | A:=B!                                         | X:=CE~!                                       | (6)Z:=X                                      |

|                                      |          |                                               |                                               | (7)X:=Z                                      |

| 14                                   | X:=W~!   | A:=X!                                         | X:=CW~!                                       | (6)SCRR!                                     |

|                                      | }        |                                               |                                               | (7)CRCR!                                     |

| 15                                   | X:=S~!   | A:=Y!                                         | X:=CS~!                                       | (6)SCRC!                                     |

|                                      | 1        | <b>,</b>                                      |                                               | (7)PANS!                                     |

|                                      | 1        | l .                                           | f                                             | •                                            |

Zig zag shift with data transfer in and out of chip

SCRR - Shift and count responders by rows

CRCR - Clear response count register

PANS - Pipelined add North to South

SCRC - Shift and count responders by columns

Fig. 1

Fig. 2

| Set all activity bits Clear Response Count Register (CRCR) For I:=1 to 64 do Shift and Count Responder (SCR) | 0.1μS<br>0.1μS<br>6.4μS |

|--------------------------------------------------------------------------------------------------------------|-------------------------|

| Turn off all chip row select lines                                                                           | 0.1µS                   |

| Turn on all chip column select lines                                                                         | 0.1µS                   |

| For I:=1 to 64 do                                                                                            | •                       |

| begin                                                                                                        |                         |

| Turn on row select line I                                                                                    | 12.8µS                  |

| Pipeline Add North to South (PANS)                                                                           |                         |

| end                                                                                                          |                         |

| For I:= to 6 do (*Empty the pipeline*)                                                                       | 0.6ըՏ                   |

| Pipeline Add North to South (PANS)                                                                           | υ.υμδ                   |

| For I:=1 to 64 do                                                                                            | 6.4 <sub>U</sub> S      |

| Pipeline Add West to East on Bottom Row Board                                                                | 0.4μδ                   |

|                                                                                                              |                         |

| Response count is now available on Bottom Row                                                                |                         |

| Board                                                                                                        | 26.6µS                  |

Pipeline Add North to South (PANS) takes the low order bit from the response count register, adds it to a data bit input on the North line and outputs the result on the South line. The carry from the addition is stored in a temporary storage cell and used in the next PANS. The input and output operations are buffered and appropriately clocked to allow true pipelined operation. Row and column select lines are turned on and off by setting and clearing bits in registers on the edge control cards. Once a row is turned on, it remains on until it is explicitly turned off and vice versa.

Fig. 3

| PADS                |                 |                                |

|---------------------|-----------------|--------------------------------|

| INSTRUCTION DECODER | ADDRESS DECODER | INSTRUCTION<br>DECODER         |

| 32 <b>PE</b> ′s     | MEMORY          | 32 PE 's                       |

| OME/<br>NONE RESPON | IDER COUNT      | EXTERNAL NEIGHBOR<br>Preselect |

|                     |                 | PADS                           |

Fig. 4

Organization of One PE

Fig. 5

|   | ZIG-ZAG          | 1 | ON-CHIP              | ALU                |     | REGISTER |   | REG | IST | ERS | 5 | SOME/ |  |

|---|------------------|---|----------------------|--------------------|-----|----------|---|-----|-----|-----|---|-------|--|

|   | NEIGHBOR CONNECT | 4 | NE IGHBOR<br>CONNECT | FUNCTION<br>SELECT | ALU | DRIVER   | Z | Y   | В   | A   | X | NONE  |  |

| \ | •                |   |                      |                    |     |          |   | _   |     |     |   |       |  |

MEMORY (32 Bits, Static RAM)

DRIVER

**MEMORY AND** MEMORY COMPARAND SELECT; DATA COMPLEMENT

ZIG-ZAG NEIGHBOR SELECT

Floorplan of One PE

Fig. 6

# An Algorithm for a Simple Image Convolution on the Titanic Content Addressable Parallel Array Processor

Charles Weems

June 1982

#### Abstract

An algorithm is presented for the Titanic Content addressable Parallel Array Processor [1] which will cause it to perform a simple image convolution very quickly. It is further shown that this algorithm can be generalized to perform more complex convolutions with only a moderate reduction in speed.

#### Background

Our previous work on Conway's Game of Life implemented on a CAM [2] demonstrated that such a device could be effectively used to speed up algorithms which dealt with rectangular grids of cells and small neighborhoods about each of those cells. Because Conway's Game of Life actually involves performing a very simple image convolution, it was soon realized that the technique developed for Life could be applied to more general convolutions. This method was further refined with the Titanic design -- a content addressable parallel array processor.

This paper is available separately as COINS Technical Report #83-07.

#### Basic Technique

One simple form of convolution involves each cell on a rectangular grid examining its immediate neighborhood and then updating its own contents based upon some function of that neighborhood. The update must, of course, be performed after all cells have finished examining their neighborhoods. On a parallel array processor this examination can be performed simultaneously by all of the cells on the grid, as can the update operation. Thus the algorithm for the convolution can be described as the actions of a single cell with the understanding that each action is performed simultaneously by all of the cells.

There are two different ways of approaching the problem of examining the neighborhood. The one that first comes to is that each cell "looks" at each cell in neighborhood, gathering what information it needs to perform an update. In practice this involves moving data from each in the neighborhood into the "central" cell where some function is then applied to it and the result stored for the update phase of the convolution. The problem with this is that the data must often pass through other cells before example, when the For cell. the central reaches neighborhood is 7x7 cells, data from the outer ring of cells must pass through at least two other cells before reaching the center cell. Because movement of data takes time, this "passing through" is rather inefficient. The solution is to have the data stored in the intermediate cells on its way to the center, thus taking advantage of the fact that those cells will also need to know the values in order to compute the function of their neighborhoods. Although this will work, the algorithm becomes rather messy since we must now consider the actions of several cells at once and how these relate to each other. It also becomes a complex problem to determine an optimal set of data collection paths as the neighborhood's diameter varies.

It turns out that the other approach to examining the neighborhood greatly simplifies these problems. This approach takes the opposite view of the collection process. Instead of each cell collecting all of the data from its neighborhood, each cell distributes its own data to every in the neighborhood. Because every other cell is also doing this, the end result is that the central cell (and hence all cells) gets the data it needs from all of the cells in the neighborhood. The problem of establishing an optimal distribution path is trivial for a square array of odd diameter: It is simply a rectangular spiral out from the center cell. For even diameter square neighborhoods the problem is only slightly more difficult because the center cell is actually half of a cell width off center in two diections. In this case it is simply required that appropriate choice of initial direction and of clockwise or counter clockwise spiral be made to select the optimal path. The only other point that requires mentioning is that, because this is a distribution process rather than a collection process, the funtion mask for the convolution must be mirrored across the central cell. For example, when the cell's value is being stored in its north neighbor, the function applied to that value is the south neighbor function. The reason for this can be seen when it is realized that the central cell is actually the south neighbor of the cell to its north. The mirroring of the convolution function mask is actually quite easy to accomplish: we simply step through the mask in exactly the opposite direction that the distribution path takes.

Let's look at an example: A simple convolution for smoothing isolated cells of noise out of an image. We will use a 3x3 convolution mask in which the cell accumulates the sum of its neighbor's values, weighted inversely with distance away from the center. The sum will then be normalized. Define the mask to be an array  $M^i$  j:

| M = |   | j | 0 | 1 | 2 |

|-----|---|---|---|---|---|

|     | i |   |   |   |   |

|     | 0 |   | 1 | 2 | 1 |

|     | 1 |   | 2 | 4 | 2 |

|     | 2 |   | 1 | 2 | 1 |

Where  $M_{1,1}$  is the central cell. Then the following algorithm will perform the convolution (north is up, west is to the left, etc.):

i := 1

j := 1

sum := value \*M;

move value north

i := i+1

sum := sum + value \* M;

move value east

j := j+1

sum := sum + value \* Mij move value south i := i-1sum := sum + value \* M<sub>i i</sub> move value south i := i-1sum := sum + value \* M move value west j:+ j-1 sum := sum + value \* M<sub>ii</sub> move value west j := j-1sum := sum - value \* M<sub>ii</sub> move value north i := i+1 sum := sum + value \* M;

value := sum \* normalizing factor

It should be noted that the time required to perform a convolution using the parallel processor is independent of the size of the image and only dependent upon the area of the convolution mask. Since the Titanic does cell level arithmetic bit-serially, the size of the data values also affects the speed of the algorithm.

# Convolution on Titanic

The following algorithm gives the list of instructions required to make Titanic perform the convolution given in the above example. In this case we have taken advantage of special characteristics in the mask values to help direct the shift and add process of the required multiply operations. The algorithm is written for 8 bit data values and runs in an estimated time of 98 microseconds.

(\* Initialize \*)

A := 1! Empty Edges

(\* Send to North \*)

```

Z := 0

For Bit := 2 to 9 do

X := M(Bit)

Shift X North

M(Bit+10) := X

Y := M(Bit -1)

Y := X+Y

M(Bit - 1) := Y

End For

X := 0

For Bit := 9 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to Northwest *)

Z := 0

For Bit := 12 to 19 do

X := M(Bit)

Shift_X_West

M(Bit) = X

Y := M(Bit - 12)

Y := X+Y

M(Bit - 12) := Y

End For

X := 0

For Bit := 8 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to West *)

Z := 0

For Bit := 12 to 19 do

X := M(Bit)

Shift_X_South

M(Bit) := X

Y := M(Bit - 11)

Y := X+Y

M(Bit - 11) := Y

End For

X := 0

For Bit := 9 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to Southwest *)

Z := 0

```

```

For Bit := 12 to 19 do

X := M(Bit)

Shift X South

M(Bit) = X

Y := M(Bit - 12)

Y := X+Y

M(Bit - 12) := Y

End For

X := 0

For Bit := 8 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to South *)

Z := 0

For Bit := 12 to 19 do

X := M(Bit)

Shift_X_East

M(Bit) := X

Y := M(Bit - 11)

Y := X+Y

M(Bit - 11) := Y

End For

X := 0

For Bit := 9 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to Southeast *)

Z := 0

For Bit := 12 to 19 do

X := M(Bit)

Shift X East

M(Bit) = X

Y := M(Bit - 12)

Y := X+Y

M(Bit - 12) := Y

End For

X := 0

For Bit := 8 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to East *)

Z := 0

For Bit := 12 to 19 do

```

```

X := M(Bit)

Shift_X_North

M(Bit) = X

Y := M(Bit - 11)

Y := X+Y

M(Bit - 11) := Y

End For

X := 0

For Bit := 9 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Send to Northeast *)

Z := 0

For Bit := 12 to 19 do

X := M(Bit)

Shift X North

M(Bit) := X

Y := M(Bit - 12)

Y := X+Y

M(Bit - 12) := Y

End For

X := 0

For Bit := 8 to 11 do

Y := M(Bit)

Y := X+Y

M(Bit) := Y

End For

(* Scale Result *)

For Bit := 2 to 11 do

X := M(Bit)

M(Bit - 2) := X

End For

M(10) := 0

M(11) := 0

980 CAM Operations

98 uS per Convolution

340 Conv / Frame Time

10204 Conv / Sec

```

Convolutions with more general and/or larger masks will take longer. A very rough worst case estimate of the time required for such convolutions can be obtained from the

formula:

$T = P(.8N+.2M+.1) + .3M(N^2P+N+1)$

where T = time in microseconds

N = number of bits in a pixel

M = number of bits in a mask value

P = number of pixels in the mask area

This is a worst case time which assumes that all of the bits in all of the mask values are ones (since this gives the slowest multiply speed). Under normal circumstances, T will about half of the value obtained from the formula. This also assumes a totally general square mask where the values If constants are to be used for the mask can change. values, a significant speed increase can be obtained by Thus, for optimizing the multiples for those values. example, a convolution on 16 bit values with 8 bit mask values could be applied over at most a 7x7 mask in one video frame time with a worst case situation. For normal situations, it should be possible to convolve a 10x10 area. Given constant mask values, and depending upon the amount of optimization possible, even a 25x25 mask could be done in one video frame time.

As a final note, this method is not restricted to square masks and in fact should be readily generalizeable to any mask shape. All that is required for this is an algorithm for efficiently shifting the center cell's value so that it covers the mask area. Thus it should be possible to easily adapt it to such mask shapes as annuli and disjoint areas.

# Conclusion

A method has been shown which can be used to program the Titanic content addressable parallel array processor to perform image convolutions simply and efficiently. Such a program, for a simple convolution, was shown which operates in ninety-eight microseconds. The time of the algorithm is independent of the size of the image and depends only upon the size of the mask and, for bit serial processing, upon the number of bits in the pixel and mask values. A formula was given for a worst case time estimate and a factor for estimating normal case time from this was discussed. It was also noted that the method could be applied to masks of other than square shapes.

# References

- 1. C. Weems, S. Levitan, and C. Foster, "Titanic: A VLSI-Based Content Addressable Parallel Array Processor, Proceedings of IEEE International Conference on Circuits and Computers, September 1982, pp.236-239.

- 2. C. Weems, "Life is a CAM-Array Old Chum", unpublished paper, January 1980.

Finding a Center of Mass with a CAM

by

Caxton C. Foster

Computer and Information Science Department

University of Massachusetts

Amherst, Massachusetts 01003

# **ABSTRACT**

Given a set of active points scattered about a plane, it is often of interest to discover the center of mass of these points. A method is presented for discovering the center of mass using a Content Addressable Memory.

# Introduction

Suppose a new disease has been reported from a number of towns across the country. Suppose an area of a picture has been identified as belonging to a particular object. Suppose the intersections of many pairs of vectors have been found. In each of these cases it might be of interest to find the centroid of the points of interest. If the points vary in mass or in reliability, we might want to give the heavier points more weight in our averaging algorithm.

Let the set of points of interest,  $P_i$ , have mass  $m_{i,k}x$ -y coordinates  $x_i$ ,  $y_i$ . What we would like to discover is the first moment of the distributions:

$$\overline{X} = \frac{\sum_{i=1}^{n} x_i m_i}{\sum_{i=1}^{n} x_i}$$

1. 1111 - 11-11- co-coni

$$\overline{Y} = \frac{\sum_{i=1}^{n} y_i m_i}{\sum_{i=1}^{n} m_i}$$

If there are n points of interest then, in general, it will require a time of order n to discover the center of mass in a conventional coordinate addressed computer. Content Addressable Memories offer a method of finding the center of mass in a time independent of the number of points involved.

# TITANIC

The machine we have called TITANIC has been described elsewhere in detail. For our purposes here it is sufficient to note that it is a content addressable memory with its cells arranged on a square grid.

Each cell thus has four spatial neighbors with which it can communicate as well as a communication path to and from the central control unit.

A cell which matches some search criterion is called a "responder".

This machine can do exact match searches, find the largest element or the smallest element of a set; it can locate the first responder or the left-most or rightmost responder in each row or the topmost or bottommost of each column, and it can count number of responders.

Two algorithms in particular should be discussed because they are central to the operation.

Global Add.

Adding up a vector is relatively simple given the Count Responders instruction in TITANIC. Assume that in each cell of the memory the number

we wish to add into the sum is stored in a field stretching from bit A (most significant) to bit B (least significant). We begin with the most significant bit and with the central variable SUM equal to zero. The algorithm proceeds as follows:

For I = A TO B

Select those cells with bit I equal to 1

X = count of the number of responders.

SUM = 2\*SUM + x

NEXT I.

As an example consider the following set of unsigned binary numbers:

1 0 1 1 = 11 0 0 0 1 = 1 0 1 0 0 = 4 1 1 0 0 = 12 0 1 1 1 = 7

number of ones

in column: 2 3 2 3

SIIM = ((2\*2+3)\*2 + 2)\*2 + 3 = 35

The Count Responders instruction takes about 20µseconds, so the sum of a vector of 8 bit numbers can be found in approximately 160µseconds independent of the number of elements in the vector.

For maximum speed global add will be micro-coded into the central controller of TITANIC.

# FIND LOCATION

In a number of problems it is convenient if a cell can discover what row (or column) it is in. Storing this information permanently in each cell is wasteful of bits and serially writing the information in each of the 512 rows (or columns) is slow. Since we wish to make the chips (and circuit cards) of TITANIC interchangeable, we do not wish to put the

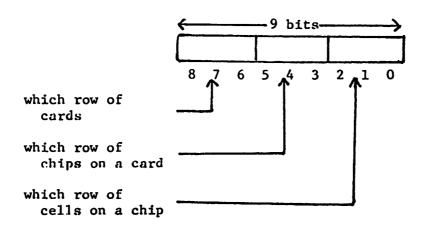

location information on board a chip or wire it into each card. The following algorithm takes advantage of the way TITANIC is designed to tell each cell its row (or column) address very rapidly.

The chips which make up TITANIC have sixty-four words arranged in an 8x8 square. It takes .9 µseconds to select the topmost row of cells on every chip and .1 µseconds to select successive rows thereafter. Writing to many cells simultaneously (multiwrite) is possible in TITANIC. It is done bit scrial-word parallel at a rate of ten bits per µsecond.

We can select the first row of cells on every chip of the memory and write 000 in the low order three bits of their address fields. This will require .9 + .3 = 1.2 pseconds. We then select the next row of cells on every chip and write 001. This will require .1 + .3 = .4 pseconds. We proceed through all eight rows on the chips writing 111 in the last row for a total of 1.2 + .4x7 = 4.0 pseconds.

Sixty-four chips are arranged on each printed circuit card in eight rows and eight columns. Circuits on the cards allow the central control unit to select any row or rows of chips for participation in an operation. The row in which a chip lies on a card will determine the middle three bits of the "row address" of that chip's cells (see Figure 1). Selecting a row of chips on each card requires .1  $\mu$ seconds, and writing three bits into the address fields of all the cells on the selected chips requires .3  $\mu$ seconds. Thus, in 8 x .4 = 3.2  $\mu$ seconds the central control unit can scan down all eight rows of chips and deposit the appropriate patterns for each row.

In a similar way, the sixty-four cards that constitute TITANIC's memory are arranged in eight rows and eight columns, and the central control unit

Figure 1. The constitution of a cell's "row address"

can select any desired combination of rows and columns of cards to participate in an operation. We select all the cells of all the chips on the first row of cards and write 000 into the high order three bits of the address fields of these cells. This takes .1 + .3 = .4 µseconds. We repeat on each successive row of cards and finish in  $.4 \times 8 = 3.2$  µseconds. When we finish the last row of cards, each cell will have all nine bits of its row address field filled with patterns ranging from 000 000 000 to 111 111 111. The total time involved is 4 + 3.2 + 3.2 = 10.4 µseconds.

A similar algorithm can be described that will insert the "column address" in the cells. Both of these algorithms will be micro coded in TTTANIC's central control unit.

# CAM ALGORITHM

Suppose that the points of interest are represented by CAM cells which are responders to a search. The location of the cell on the machine grid is the analogue of the X Y coordinates we wish to average. Such a situation might readily arise if a picture has been mapped onto the CAM with each pixel occupying one memory cell.

To find the value of X we first find the total "mass". We begin by setting the "activity bit" (A) of those cells that contain points of interest. The design of TITANIC is such that only those cells with A=1 will participate in operations.

- 1. We perform "Global Sum" on the MASS fields of the participants. Let this sum equal M.

- 2. We execute a FIND ROW LOCATION, putting the row address in a cell field called ADDR.

3. For all participants in parallel we multiply MASS times ADDR and put the product in P.

This cell parallel operation is performed bit serially by shift and add. Each bit addition takes .4  $\mu$ seconds, so the product of two eight bit fields can be calculated in  $64x.4 = 25.6 \mu$ seconds.

- 4. We do a "Global Sum" of the products. Call this P.

- 5. The center of mass will be located on the row given by P/M.

- 6. Repeat steps two through five for the column addresses and we will have the column on which the center of mass is located.

The timing for this algorithm is as follows.

| Find EM                           | 160    | x   | 1 | = | 160   |

|-----------------------------------|--------|-----|---|---|-------|

| Find Row                          | 10.4   | x   | 2 | = | 20.8  |

| Multiply                          | 25.6   | ×   | 2 | = | 51.2  |

| Find $\Sigma P$ (16 bit products) | 320    | ×   | 2 | = | 640   |

| Total time in micro               | o seco | nds | 3 | = | 872.0 |

In a conventional von Neumann machine we must fetch each cell, decide whether it is a participant and the perform a multiplication and an addition.

Letting R=1 for participants and 0 otherwise, then the program below will discover the center of mass:

```

1 FOR I = 1 TO 512

2 FOR J = 1 TO 512

3 IF R(I,J)=0 GOTO 7

4 MASS = MASS + M(I,J)

5 XP = XP+I*M(I,J)

6 YP = YP+J*M(I,J)

7 NEXT J

8 NEXT I

```

Given the most efficient compiler, this will require  $3x2^{18}$  additions and  $2*2^{18}$  multiplications. The reader is welcome to make his own assumptions about the time required for an add and for a multiply, and to calculate a time to find the center of mass. Assuming all cells are active and one  $\mu$ second for each operation brings the total time to roughly  $5x2^{18}$  or one and one-quarter seconds.

## CONCLUSIONS

The TITANIC has been shown to be about 1,400 times faster than a RAM in computing the center of mass given reasonable assumptions. The reason it is not 2<sup>18</sup> times as fast is that the individual operations in a CAM takes many times as long as they do in a RAM because they are performed bit serially. It is interesting to note that the time required for a CAM is the same no matter how many active cells are involved. In a RAM storing data in compressed vectors will allow the time to depend linearly on the number of active cells. Again assuming 1 µsecond adds and multiplies, it will take 5 µseconds to process each active cell. If there are fewer than two hundred active cells and if the data can indeed be stored properly, the RAM will be faster than the CAM.

# DETERMINATION OF THE ROTATIONAL AND TRANSLATIONAL COMPONENTS OF A FLOW FIELD USING A CONTENT ADDRESSABLE PARALLEL PROCESSOR

M. E. Steenstrup, D. T. Lawton, C. Weems

Department of Computer and Information Science<sup>1</sup>

University of Massachusetts at Amherst

## **Abstract**

The realization of motion perception in artificial systems will require highly parallel architectures. Here we demonstrate the use of a Content Addressable Parallel Processor (CAPP) [1,2] as an effective means of quickly and accurately decomposing a flow field into its rotational and translational components [3] to recover the parameters of sensor motion.

# Organization of the CAPP

The CAPP is a VLSI-based Single Instruction Multiple Data (SIMD) machine designed at the University of Massachusetts [4]. It consists of a parallel processor containing 512x512 cells and a central controller. The central controller issues instructions to the parallel processor, controls loading and unloading of data in the parallel processor, and serves as an interface to the host computer and to secondary storage devices. It broadcasts data to the parallel processor bit serially, and the entire memory may be bulk-loaded in one video frame time (1/30 second). The central controller contains a set of micro-coded subroutines in ROM for performing high-level CAPP routines and a writeable control store for adding microcode.

The parallel processor consists of an 8x8 array of processing circuit boards and a set of boards which control CAPP edge treatment. Each processor board, in turn, consists of an 8x8 array of special purpose CAPP IC chips plus random buffer logic. Each chip then contains 64 cells, an instruction decoder, and some miscellaneous logic. There are eight basic instruction types recognized by the chip, each performed in parallel by the constituent cells. Most instructions take one minor cycle time (100 nanoseconds) to execute. Inter-cell communication is bit serial and is accomplished by a four-way (N, S, E, W) cell interconnect network, allowing for three types of edge treatments: dead-edging, circular wrap, and zig-zag wrap.

Each unit cell consists of 64 bits of fully static memory, four one-bit static "tag" registers A, B, X, and Y, a static carry bit register Z, and an ALU which continuously generates X NAND Y, X NOR Y, and X + Y + Z. Also, each cell contains logic for selecting a data source (a register (excluding Z), memory, an ALU function, broadcast data, or a neighboring cell (N, S, E, or W)), possibly inverting the selected signal, and storing it in a destination (a register or memory). The X register is the main tag register. Its output is connected to Some/None logic, indicating cell response, and to the neighbor communication network. The A register controls whether or not a cell is active. An inactive cell ignores all but a small set of instructions broadcast by the central controller. The Y register provides a secondary store for tag bits, while the B register provides a secondary store for activity bits.

# Flow Field Decomposition Procedure

Our algorithm is an exhaustive search procedure which uses a set of rotational and translational flow field templates to find a component pair which can account for the motion depicted in a given flow field. Currently, 1000 rotational templates and 200 translational templates are used. These are generated from 100 axes which are uniformly distributed with respect to a unit hemisphere, and all pass through the origin of the sensor coordinate system. Each flow field consists of 16x16 vectors and is stored on a 2x2 square of chips consisting of 256 cells. The 2x2 chip arrangement facilitates flow field addressing. Each cell contains the horizontal and vertical components of a flow vector, each specified with 10 bits of precision.

The algorithm consists of four basic steps.

- (0) The rotational templates are loaded into the CAPP, one template for each flow field location. Each flow field location corresponds to one of the squares in the CAPP diagrams shown in Figures 2a, 2b, and 2c. The rotational templates need only be loaded once since they are used in determining any flow field decomposition.

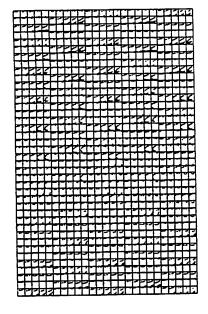

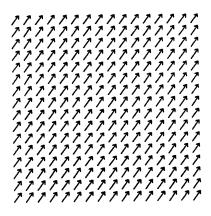

- (1) A copy of the input flow field is loaded into each flow field location in the CAPP. Figure 1a and 1b show two sample input fields, both produced by the same motion and environment, except that Figure 1b was produced by adding random spike noise to Figure 1a.

This research was supported by DARPA under Grant N00014-82-K-0464.

- (2) A set of difference fields is formed by subtracting each rotational template from the copy of the input flow field stored with it. For each resulting difference field, the slope of each difference vector is computed by dividing the vertical component by the horizontal component. These subtraction and division procedures are performed in parallel across all flow fields represented in the CAPP.

- (3) The similarity between the difference fields and each of the translational templates is evaluated, proceeding sequentially through all the translational templates. For a given translational template, this comparison is done in parallel with all difference fields stored in the CAPP and consists of the following steps:

- (3a) The slope of each component vector of the translational template is loaded into the corresponding vector location of each difference field. The sign of the slope of each difference vector is compared with the sign of the slope of the corresponding translational template vector. If the signs agree, the absolute value of the difference between the slope of the difference vector and the slope of the translational template vector is computed, and then scaled according to the absolute value of both slopes. If the scaled slope difference does not exceed a predetermined maximum error value, then a vector match is designated at that position. The quantity of error permitted here allows the algorithm to be resistant to uniformly distributed Gaussian noise of low variance present in the original flow field.

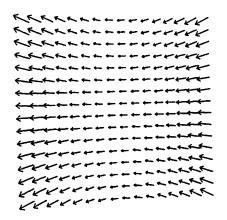

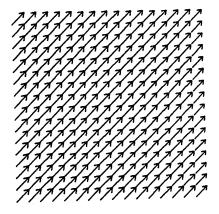

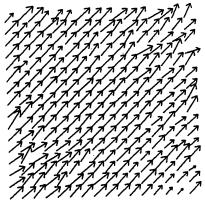

- (3b) For each difference field the number of vector If this sum exceeds a slope matches is counted. predetermined minimum number of matches (in our implementation, 75% of the field size), then the associated rotational and translational templates become a candidate pair for the flow field decomposition. Utilization of a minimum number of required matches ensures that only templates which are reasonably close to the actual motion will be chosen and permits some resistance to random spike noise. Figure 2a shows, for difference fields resulting from the input field in Figure 1a, the CAPP response to the translational template which is closest to the actual translational motion. Each black dot within a square represents a position in a difference field at which the slope of the difference vector matches the slope of the translational template. Figure 2b shows, for difference fields resulting from the input field in Figure 1b, the CAPP response to the translational template which is closest to the actual translational motion. Figure 2c shows the CAPP response to a translational template which is not close to the actual translational motion. This translational template is shown in Figure 3.

- (3c) For all difference fields yielding at least the required minimum number of matches, the variance of the scaled slope difference is computed, and the difference field with the minimum variance is determined. This value is compared to the minimum variance found from processing the preceding translational templates. If this value is less than the preceding minimum, it becomes the new global minimum, and the rotational template associated with the difference field together with the

current translational template become the current best candidate pair for the flow field decomposition.

Steps 3a, 3b, and 3c are performed for each translational template.

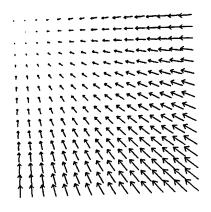

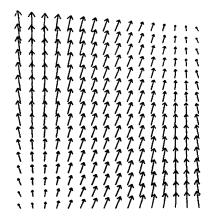

(4) The flow field decomposition considered to be the best is the rotational and translational template pair resulting in the difference field yielding at least the required minimum number of matches and the least slope difference variance. Utilizing minimum variance instead of the maximum number of matches, the algorithm has achieved better results, particularly for motions whose component parts lie between sets of templates. Figures 4a and 4b show the rotational and translational templates selected by the algorithm in the presence of and in the absence of noise, for the input fields in Figures 1a and 1b. These templates are the closest ones to the actual motions. Figures 5a and 5b show the difference fields resulting from subtracting the rotational motion in 4a from the original fields in Figures 1a and 1b respectively.

## **Experiments**

Experiments have been performed with a CAPP simulator on a VAX 11/180 using a wide variety of motions and simulated environments. In all cases examined, the translational template closest to the actual translational motion was selected. The rotational template was always close to the actual rotational motion, but was sometimes not the closest template. The procedure proved to be resistant to limited Gaussian noise as well as to limited random spike noise in the original flow field. Applying motion to points at random depths produced results similar to those obtained in the noise experiments. The algorithm's performance degraded slightly if each flow vector component was specified by eight bits of precision instead of by ten.

The CAPP timing calculations revealed that the algorithm could perform the rotational-translational decomposition in slightly more than 1/4 second. If two CAPPs are used in parallel, then the time can be reduced to less than 1/5 second, since only half of the translational templates need be tested on each CAPP. Given fabrication techniques available in the immediate future, we expect execution times to be significantly improved. We also suspect that performance will improve by increasing both the number and size of the rotational and translational templates. This amounts to utilizing more CAPPs in parallel.

# References

- [1] Foster, Caxton C. Content Addressable Parallel Processors. Van Nostrand Reinhold, New York, 1976.

- [2] Lawton, D.T., Steenstrup, M.E., Weems, C. "Determination of Rotational and Translational Components of a Flow Field using a Content Addressable Parallel Processor", COINS Technical Report, Computer and Information Science Department, University of Massachusetts, February, 1983.

Figure 2c

Figure 4a

Figure 5a

Figure 3

Figure 4b

Figure 5b

[3] Prazdny, K. "Determining the Instantaneous Direction of Motion from Optical Flow Generated by a Curvilinearly Moving Observer." Proc. of the Pattern Recognition and Image Processing Conference. Dallas, Texas, August 1981, pp. 109-114.

[4] Weems, C., Levitan, S., and Foster, C. "Titanic: A Content Addressable Parallel Array Processor for Image Processing." IEEE International Conference on Circuits and Computers. New York, September 1982.

Figure 1a

Figure 2a

Figure 1b

Figure 2b

Extracted from: "Incorporating content addressable array processors into computer vision systems"; 27th Annual International Technical Symposium & Instrument Display, August 21-26, 1983, San Diego, California; Charles Weems and Daryl T. Lawton

# Associating symbolic descriptions with segmentations

A basic step in the functioning of autonomous, general purpose vision systems is the association of low level, spatially organized, symbolic descriptions with the results of segmentation, region and edge extraction processes (for example, the Primal Sketch [1] and the Regions-Segments-Vertices RSV representation of the VISIONS system [2]). Such a representation acts as a data base which is accessed by various recognition processes to determine the relations between different image strucutres. We have analyzed the implementation of some simple segmentation procedures using the CAAPP, such as zero-crossing extraction after convolution with a Gaussian-Laplacian mask [1] and histogram-guided segmentation Both these procedures are very rapid and are selectively sensitive to [3]. image information at different spatial frequencies and contrasts. We have found that associating symbolic information with the results of these segmentation procedures is most effective when the CAAPP is used in two different ways. one of these, the symbolic labelling takes place in the same memory locations where the segmentation is, in parallel accross the CAAPP. In the second, a test performed at a specified location for a particular type of image structure. If the test is successful at that location, the occurrance of the resulting image structure is stored in a network residing in another CAAPP. symbolic data base is stored in a CAAPP, its associative character is used to make the extraction of complex structural relations possible [4].