## IMAGE PROCESSING ON A CONTENT ADDRESSABLE ARRAY PARALLEL PROCESSOR

Charles C. Weems, Jr.

COINS Technical Report 84-14

September 1984

This research was supported in part by the Army Research Office under grant number DAAG 29-79-G-0046, the Defense Advanced Research Projects Agency under contract N00014-82-K-0464, General Electric Company (Flexible Automation Systems Program, Corporate Research and Development), and Digital Equipment Corporation.

# IMAGE PROCESSING ON A CONTENT ADDRESSABLE ARRAY PARALLEL PROCESSOR

A Dissertation Presented

Ву

Charles Chilton Weems Jr.

Submitted to the Graduate School of the University of Massachusetts in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September 1984

Department of Computer and Information Science

# IMAGE PROCESSING ON A CONTENT ADDRESSABLE ARRAY PARALLEL PROCESSOR

A Dissertation Presented

Ву

Charles Chilton Weems Jr.

Approved as to style and content by:

Dr. Caxton C. Foster, Chairperson of Committee

Liver Licena

Dr. Edward M. Riseman, Member

Dr. D. Nico Spinelli, Member

Dr. Charle R. Rupp Member

Dr. David W. Stemple, Graduate Program Director Department of Computer and Information Science

Charles Chilton Weems Jr.

0

All Rights Reserved

Research supported in part by:

Army Research Office DAAG 29-79-G-0046.

DARPA N00014-82-K-0464.

General Electric Company, Flexible Automation Systems

Program, Corporate Research and Development.

Digital Equipment Corporation.

Dedicated To The Memory Of

Herman Gotloeb Herrmann

#### ACKNOWLEDGEMENT

There are many people who have helped me along the road to writing this dissertation. In particular I would like to thank my committee: Nico Spinelli, for his helpful suggestions, especially with regard to reviewing literature; Charle' Rupp, for teaching me most of practical things I know about VLSI; and Edward Riseman, his many suggestions and a great deal of help with the computer vision aspects of this work. Most of all I would like to thank my advisor, mentor and friend, Caxton Foster. Over the past five years I have learned a great many things from him, some technical in nature and some not. I feel very proud to be able to call myself one of his students.

In addition to my committee, there are many people who have directly assisted me in this research. I would like to thank Al Hough, Daryl Lawton, Martha Steenstrup, Jeff Bonar, Raj Wall, John Adler, Steve Weiss, Ken Estabrook, Kurt Rudahl, and Madhura Kirloskar for their contributions. I would especially like to thank Steve Levitan. He has been a constant source of ideas, encouragement, help, sage advice and moral support for these five years. I am most indebted to Bill Verts, my very good friend and fellow Oregonian, who has kept me from going insane on many an occasion.

I would also like to thank the people who have really made this all possible, the secretaries and staff who do so much to keep life at the University running smoothly: Ruth Morrell, Rose Korowski, Renee Stephens, Louise Till, Bonnie Cichy, Barbara Gould, Janet Turnbull, Susan Parker, Renita Ballard, Rick Newton, Skip Rochfort, and Joey Griffiths.

Three of my former teachers, Robert Anderson, Gene Enfield and Harry Goheen have had a particularly strong influence on the course of my academic career. They are the people who are most responsible for my choosing the path that I have taken.

Most of all, I would like to thank my Mother for her support, encouragement and love.

#### **ABSTRACT**

Image Processing on a Content

Addressable Array Parallel Processor

August, 1984

Charles Chilton Weems Jr., B.S., M.A., Oregon State

University, PhD., University of Massachusetts

Directed by: Professor Caxton C. Foster

We present the design of a Content Addressable Parallel Processor (CAAPP) for image processing and low to intermediate level vision processing. This new architecture combines: a) associative processing including global broadcast and response to and from the array of cells, and b) array processing via local square neighborhood This combination of capabilities can be used computation. to close the feedback loop between high and low level vision by providing appropriate and mechanisms for bidirectional information flow between the its host symbolic processor. A number CAAPP and algorithms are presented which demonstrate this.

The CAAPP design consists of a square array of 512 by 512 processors, with its own controller, driven by a host processor. The basis of the hardware design is a custom VLSI chip which contains 64 bit-serial processors. We have taken a pragmatic view of fabrication technologies (VLSI,

packaging, etc.), approaching the design very conservatively. The architecture does, however, represent a genuine increase in processing power over the best machines now available. The design of a test chip with 16 processors is presented to demonstrate the feasibility of construction with current technology.

The experience needed to achieve an effective CAAPP design was attained by iterative evaluation and redesign. The evaluations consisted of developing algorithms with a subsequent analysis of architectural effectiveness. Two iterations of the development process are presented here. The first is our experience with a commercially available system. The second is the analysis of our first CAAPP design, based on simulations that gave us statistics for static and dynamic instruction set usage. The result is three new designs, based on the capabilities of three potential fabrication technologies.

Several of the parallel algorithms developed as part of the evaluation process are, themselves, of considerable interest. These include a method of decomposing rotational and translational motion parameters from an optic flow vector field, an order square-root of N sorting algorithm, and a way of performing LISP garbage collections that insures the capability of real-time response.

## TABLE OF CONTENTS

| ACKNO<br>ABSTF<br>LIST<br>LIST | RACT  | • .          |         |            |          | •   |      |           |              |          |           |     |      |            |        |            |       | _            |          | _         | _   | _        | _ | ٠,١ | ı i |

|--------------------------------|-------|--------------|---------|------------|----------|-----|------|-----------|--------------|----------|-----------|-----|------|------------|--------|------------|-------|--------------|----------|-----------|-----|----------|---|-----|-----|

| СНАРТ                          |       | INDU         |         | •          | •        | •   | •    | •         | •            | •        | •         | •   | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • | • 2 | ٠.٧ |

| _                              | _     |              |         |            |          |     | _    |           |              |          |           | _   |      |            |        |            |       |              |          |           |     |          |   |     |     |

| I.                             | 1     | NTRO         | ניטטכ   | .10        | N        | AN  | D    | OV        | ER           | IVI      | ΕW        | I   | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • | •   | ]   |

|                                |       | The<br>The   | Vis     | sio        | n        | Pr  | ob   | 16        | m            | •        |           | •   |      |            | •      |            | •     | •            | •        | •         | •   | •        | • |     | 2   |

|                                |       | The          | Arc     | chi        | te       | ct  | ur   | e         | Pr           | ob       | 16        | m   |      | •          | •      | •          | •     | •            | •        |           | •   | •        |   |     | 8   |

|                                |       | The          | Enc     | gin        | ee       | ri  | ng   | ı E       | ro           | bl       | .en       | 1   |      |            |        |            | _     |              | _        |           | _   |          |   | . 1 | L 1 |

|                                |       | The<br>The   | Exp     | er         | ie       | nc  | e Î  | Pr        | ob           | le       | m         |     |      |            |        |            | •     | •            | •        |           |     |          |   | . 1 | 13  |

|                                |       | The          | Cor     | ntr        | ib       | ut  | io   | ns        | 6 0          | £        | th        | nis | ; ]  | Res        | sea    | arc        | ch    |              |          |           |     |          |   | . ] | L 4 |

|                                |       |              |         |            |          |     |      |           |              |          |           |     |      |            |        |            |       |              | -        | -         | -   | -        | • | -   |     |

| II.                            | . A   | REV          | IEW     | OF         | A        | SS  | 00   | IA        | TI           | VE       | . P       | ND  | ) ]  | PAF        | RAI    | LLI        | ΞL    | P            | 300      | CES       | SSC | RS       | 3 | . ] | L 9 |

|                                |       |              | _       |            |          |     |      |           |              |          |           |     |      |            |        |            |       |              |          |           |     |          |   |     |     |

|                                |       | Int:<br>Def: | codi    | ıçt        | io       | n   | •    | •         | •            | • .      | •         | •   | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • | • ] | L 9 |

|                                |       | Defi         | init    | :10        | ns       | 0   | £    | Αs        | SSO          | Ci       | at        | :iv | 7i   | tу         | •      | •          | •     | •            | •        | •         | •   | •        | • | . 2 | 20  |

|                                |       | What<br>A Da | t CA    | M'         | S        | ar  | е    | Us        | ed           | F        | 'or       | •   | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • | . 2 | 2]  |

|                                |       | A Da         | atak    | pas        | e        | Se  | ar   | ch        | E            | Хa       | mE        | ole | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • | . 2 | 27  |

|                                |       | Fine         | ding    | j G        | re       | at  | es   | it        | an           | d        | Le        | as  | ١t   | •          | •      | •          | •     |              | •        |           |     |          |   | . 3 | 3 1 |

|                                |       | Some         | e Dr    | aw         | ba       | ck  | s    | οf        | : C          | 'AM      | l's       | 5   |      | _          | _      |            | _     | _            | _        | _         | _   |          | _ |     | 3 2 |

|                                |       | Cont         | tent    | : A        | dd       | re  | SS   | ab        | ole          | P        | ar        | al  | .16  | <b>e</b> l | Pı     | 00         | ces   | ss           | ors      | 3         |     |          | _ | . 3 | 3 4 |

|                                |       | Some<br>The  | e CA    | PP         | 0        | pe  | ra   | ti        | .on          | s        |           |     |      |            |        |            | _     | _            | _        | •         | _   |          | • |     | ₹6  |

|                                |       | The          | Add     | l C        | om       | pa  | ra   | nd        | l A          | la       | or        | it  | :hr  | 'n         | •      |            |       |              |          | •         | •   | •        |   | . : | 27  |

|                                |       | The          | Add     | F          | ie       | id  | s    | Al        | αo           | ri       | th        | ım  |      |            | -      | •          | •     | •            | Ĭ.       | •         | •   | •        | • | • - | ? ¢ |

|                                |       | Тур          | ical    | C          | AΡ       | P   | Ar   | ם<br>1 מנ | ic           | at       | ·ic       | ns  | : ,  | and        | , ,    | ?ns        | , i r | or           | ·<br>nm4 | •<br>an t | •   | •        | • | • - | , c |

|                                |       | A S          | 17 V.   | - V        | o f      | - Δ | 55   | 000       | ·i a         | + i      | . T C     |     | r    | 2006       |        | 3<br>3.0.1 | , T.  | . 01         | 11110    | =11(      | . 3 | •        | • | • • | 1 · |

|                                |       | The          | Can     | ry<br>ni o | n i      | ~6  | פ    | EN        | . <u>.</u> . |          | . • •     | ٠ . | _ `  |            |        | , ,        | . 3   | •            | •        | •         | •   | •        | • | • • | 2 Z |

|                                |       | A Re         | Sei     | 11.7       | ~ £      | C D | מ כי | 1         | 1<br>1 ~     | .1       | •<br>D~   | •   | •    | •<br>• • • | •      | •          | •     | • ,          | •        | •         | •   | •        | • | . 4 | ł 4 |

|                                |       | SIMI         | ) D-    | . w        | ) i      | _ F | a r  | aı        |              | . T      |           |     | :e:  | 221        | . II . | ) (        | 111C  | 1 1          | 720      | ) C E     | 255 | 50 I     | S |     |     |

|                                |       | SIMI         | ) Po    | ıra        | T T      | СI  | r    | LC        | Ce           | 55       | OL        | . 5 | T    | JL         | 10     | uaç        | Jе    | PI           | 00       | ces       | SS  | ınç      | 3 | • 5 | ) 4 |

| TTT                            | . п   | HE SI        | on to   | ) AT TA    | ~ c      | ם   | EM   |           | 7            | NT.      | E V       | 705 | יםי  | IME        | יזאי   | רא ז       | . ,   | <b>י</b> א כ | מ כ      | Co        |     | <b>.</b> |   |     |     |

|                                | . • • | IN           |         |            |          |     |      |           |              |          |           |     |      |            |        |            |       |              |          |           |     |          |   |     | : 0 |

|                                |       | 111          |         |            | •        | 110 | D I  | L         | , 57         |          |           |     | ,,,, |            | •      | •          | •     | •            | •        | •         | •   | •        | • | • - | ) > |

|                                |       | Inti         | codi    | ict        | iο       | n   | _    | _         |              |          |           |     |      |            |        |            |       |              |          |           |     |          |   | . 5 | : 0 |

|                                |       | Post         |         |            |          |     |      |           | · a          | Ba       | 56        | •   | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • |     |     |

|                                |       | 7            | Arch    | 1 i +      | ے<br>مم  | +11 | ra   | 1         | .u<br>.a:,   | ם<br>ובי | ם.<br>פנו | + i | •    | •          | •      | •          | •     | •            | •        | •         | •   | •        | • | .6  |     |

|                                |       | Real         | n i     | me.        | G C<br>T | TC  | L a  | Tr        | +~           | aı       | ua<br>v   |     |      |            | •      | •          | •     | •            | •        | •         | •   | •        | • | .6  |     |

|                                |       | Real         | / ~ ~ P |            | ~ ~      | T 2 | ~ ~  | J<br>TII  | 2            | τ'n      |           | ا د | : L  | •          | •      | •          | •     | •            | •        | •         | •   | •        | • |     |     |

|                                |       |              | Arch    |            |          |     |      |           |              |          |           |     |      |            | •      | • .        | •     | •            | •        | • .       | •   | •        | • | . 6 |     |

|                                |       | Cry          | can     | ıaı        | ys       | 15  | 0    | I         | 51           | wb       | те        | S   | u    | ost        | : 1 t  | ut         | :10   | n            | C        | ιph       | ıeı | S        | • |     |     |

|                                |       | Æ            | Arch    | 11 t       | ec       | tu  | ra   | Ι.        | ev           | al       | ua        | ti  | or.  | 1          |        |            |       |              |          |           | _   | _        | _ | . 6 | : 7 |

| <b>.</b>                                                                       |           |

|--------------------------------------------------------------------------------|-----------|

| Real Time Tune Recognition                                                     | 6'        |

| Architectural evaluation                                                       | _         |

| John Conway's Camp of Tife                                                     | • • • • • |

| John Conway's Game of Life  Architectural evaluation  Text to Speech Synthesis | 6         |

| Architectural evaluation                                                       | 7         |

| Text to Speech Synthesis                                                       | 7         |

| Architectural evaluation                                                       | 7         |

| Summary of Findings                                                            | 7         |

|                                                                                | • • / 3   |

| TV DEGLEV DOD - CONTINUE                                                       |           |

| IV. DESIGN FOR A CONTENT ADDRESSABLE ARRAY PARALLE                             | L         |

| PROCESSOR                                                                      | 81        |

|                                                                                | • • • •   |

| Introduction                                                                   |           |

| Introduction                                                                   | 85        |

| Design Constraints.                                                            | 0.6       |

| Design Goals                                                                   | 92        |

| The CAAPP                                                                      | 101       |

| The controller                                                                 | • 101     |

| The distribution of 200                                                        | • TO      |

| The distribution of 262,144 processing                                         |           |

| elements                                                                       | . 104     |

| Processing elements                                                            | . 107     |

| The registers                                                                  | 111       |

| Neighbor communications                                                        | • 111     |

| Register Communications                                                        | • 113     |

| Broadcast comparand and memory data                                            | . 113     |

| Activity control                                                               | . 119     |

| Some/none and response count                                                   | 116       |

| The array edge direction.                                                      | • 11.     |

| The array edge circuitry                                                       | • 121     |

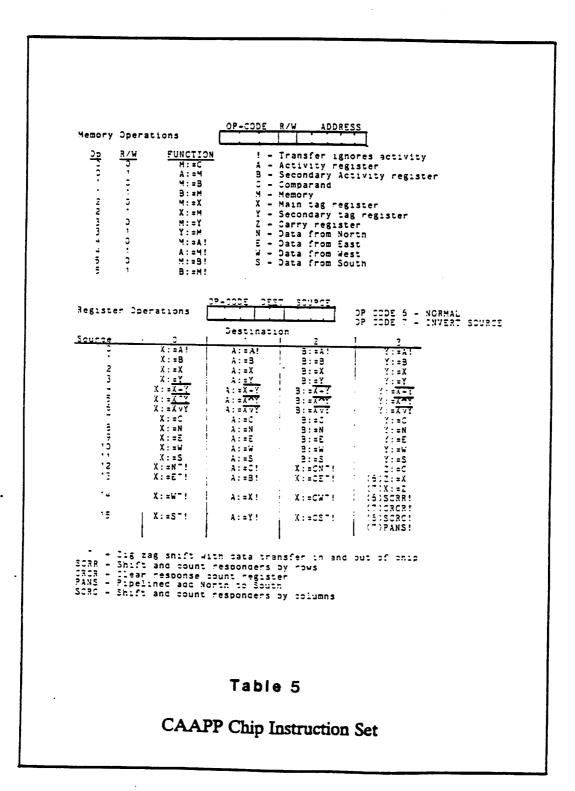

| The Processing Element Instruction Set                                         | . 122     |

| Memory operations                                                              | . 124     |

| Register operations                                                            | . 125     |

| Communications operations                                                      | • 14.     |

| Charial around operations                                                      | . 126     |

| Special operations                                                             | . 128     |

| The CAAPP Simulator                                                            | . 129     |

| Circuit Board Layout                                                           | 132       |

| The Special Purpose CAAPP Integrated Circuit                                   | 12/       |

| CAARD ship of carriers                                                         | • 134     |

| CAAPP chip pin assignments                                                     | • 135     |

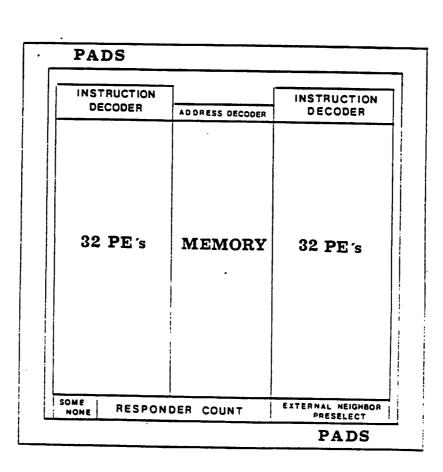

| CAAPP Chip overall floorplan                                                   | . 135     |

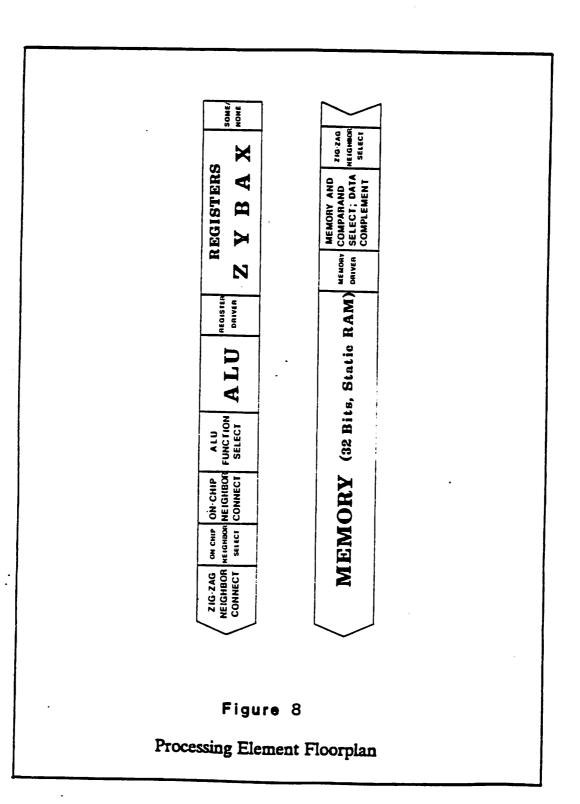

| Processing element floorplan                                                   | . 141     |

| Support circuitry                                                              | 1/3       |

| Processing element circuitry                                                   |           |

| Company the little Circuity                                                    | . 162     |

| Summary statistics                                                             | . 188     |

| Memory simulation and fabrication                                              | . 189     |

| Design Conclusions                                                             | . 194     |

|                                                                                | • 17      |

| V. APPLICATIONS AND ANALYSIS                                                   |           |

| V. APPLICATIONS AND ANALYSIS                                                   | . 195     |

|                                                                                |           |

| Introduction                                                                   | . 195     |

| Introduction                                                                   | . 199     |

| Count responders                                                               | 100       |

|                                                                                | 202       |

| Greater and less than searches             | . 204        |

|--------------------------------------------|--------------|

| Greatest and least searches                | . 206        |

| Select first                               | . 208        |

| Add and subtract constant                  | . 214        |

| Add and subtract fields                    | . 215        |

| Multiply by constant                       | . 217        |

| Divide by comparand                        | 219          |

| Multiply fields                            | . 221        |

| Divide fields                              | . 223        |

| Simple Image Processing Operations         | . 228        |

| Game of life                               |              |

| Gaussian smoothing image convolution       | . 234        |

| Sobel edge extracting operation            | . 245        |

| Histogram                                  |              |

| Rotate 3-D model and extract frontal       | . 231        |

| surface                                    | 25/          |

| Higher Level Image Processing Operations   | 267          |

| Region growing and labelling               | 202          |

| Decomposition of rotational and            | . 204        |

|                                            |              |

| translational motion parameters from       | 260          |

| optic flow                                 | . 269        |

| Other Applications                         | . 288        |

| Center of mass                             | . 289        |

| Geocorrection of satellite images          | . 293        |

| Square grid sort                           | . 299        |

| Real time execution of LISP programs       | . 305        |

| Simulation of neural networks              | , 311        |

| Graph processing and semantic networks     | , 313        |

| VI. EVALUATION AND REDESIGN                | . 319        |

| Introduction                               | 310          |

| Statistical Summary of Algorithms          | , 31)<br>301 |

| Discussion of Instruction Set Usage        | 325          |

| Summary of Findings                        | 220          |

| Other Possible Architectural Enhancements  | , JJ0        |

| Memory size                                | , 341        |

| Memory size                                | , 341        |

| Faster response count                      | 343          |

| Expansion of the ALU inputs                | 344          |

| Ability to complement All inputs           | 347          |

| Ability to complement ALU inputs           | 348          |

| Full width interchip communications        | 349          |

| Long distance communications between cells |              |

| Vector broadcast registers                 | 354          |

| Direct selection of individual cells by    |              |

| the controller                             | 355          |

| Build chips from 16 cell blocks of         |              |

| processors                                 | 355          |

| Dual ported cell memory                                                | 356   |

|------------------------------------------------------------------------|-------|

| """ LIBIT ALU LESUIT GESTINATIONS                                      | 250   |

| Multiple Controllers connected to subarrant                            | 250   |

| Evaluation of the proposed Enhancements                                | 262   |

| Conservative Second Design                                             | . 363 |

| Conservative Second Design  Design constraints  Overview of the design | 368   |

| Overview of the docier                                                 | 368   |

| Overview of the design                                                 | 369   |

| Chip and processing element design features                            | 369   |

| Design advantages and limitations                                      | 377   |

| impiementation analygie                                                | 270   |

| comparison to the previous design                                      | 201   |

| intermediate second pesign                                             | 201   |

| beergn constraints .                                                   | 201   |

| overview of the design                                                 | 201   |

| Chip and processing element design features                            | 202   |

| ine new response count mechanism                                       | 200   |

| Design advantages and limitations                                      | 202   |

| Implementation analysis                                                | 392   |

| Comparison to the previous designs                                     | 393   |

| Advanced Second Design                                                 | 395   |

| Design constraints                                                     | 39/   |

| Overview of the design                                                 | 397   |

| Overview of the design                                                 | 398   |

| Chip and processing element design features                            | 399   |

| Design advantages and limitations                                      | 402   |

| Implementation analysis                                                | 404   |

| Comparison to the previous designs                                     | 404   |

|                                                                        | •     |

| VII. CONCLUSIONS                                                       | 408   |

|                                                                        |       |

| VIII. FURTHER RESEARCH                                                 | 116   |

|                                                                        | 410   |

| • • • • • • • • • • • • • • • • • • • •                                |       |

|                                                                        | •     |

| BIBLIOGRAPHY                                                           | 400   |

|                                                                        | 420   |

| APPENDIX A: A HISTORICAL REVIEW OF ASSOCIATIVITY                       |       |

| MIT DADIA A. A MISTORICAL REVIEW OF ASSOCIATIVITY                      | 431   |

| Waxly Concentions of Association                                       |       |

|                                                                        | 431   |

| MEMEX                                                                  | 433   |

| Cryotron Catalog Memory                                                | 433   |

| Associative Processor and APP                                          | 436   |

| GAP or the RADC 2048 word CAM                                          | 438   |

| NEBULA                                                                 |       |

|                                                                        | 444   |

|                                                                        | 449   |

|                                                                        | 454   |

| Company 1 Commany 1 -                                                  |       |

| General Comments                                                       | 456   |

| APP | ENDI   |             | 3:    | A      | H   | IS  | TO  | RI  | C   | ΑL   | R   | EV | ΙE   | W ( | OF  | S | IMI | ) 1 | PAI | RAI | LLI | ΞL |   |   |   |     |

|-----|--------|-------------|-------|--------|-----|-----|-----|-----|-----|------|-----|----|------|-----|-----|---|-----|-----|-----|-----|-----|----|---|---|---|-----|

|     | PROC   | ESS         | SOR   | S      | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 460 |

|     | von    | Net         | ıma   | nn     | 's  | С   | el  | 1 t | ıla | ar   | C   | om | pu · | te  | r   | • |     |     |     |     |     |    |   |   |   | 460 |

|     | The    | Spa         | ati   | al     | C   | mc  | pu  | te  | r   | •    |     | •  | •    | •   | . • |   |     |     | •   | •   | _   | •  | • |   |   | 461 |

|     | Holl   | and         | i's   | M      | aci | hi  | ne  |     |     |      |     |    |      |     |     |   | •   |     | •   | •   | •   |    | · | • | • | 462 |

|     | The    | Ort         | ho    | go     | na: | 1 1 | Co  | mr  | ut  | e:   | ď   | •  | •    | •   | •   | _ | •   | •   |     | ·   | •   | •  | • | • | • | 161 |

|     | SOLO   | MON         | J T   | _      |     |     |     |     |     |      | ٠.  | •  | Ī    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 165 |

|     | SOLO   | MON         | JT    | т      | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 400 |

|     | TITT   | יוייי<br>אר | ` T T | т<br>Т | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | ٠   | •   | •  | • | • | • | 4/4 |

|     | ILLI   | AC          | 11    | 1      | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 474 |

|     | ILLI   | AC          | ΤΛ    |        | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 472 |

|     | PEPE   | •           | •     | •      | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 474 |

|     | OMEN   |             | •     | •      | •   | •   | •   | •   | •   | •    | •   | •  | •    | •   | •   | • |     | •   |     | •   |     | •  |   |   |   | 478 |

|     | CLIP   | 3           | •     | •      | •   | •   | •   | •   | •   | •    | •   |    | •    | •   |     | • |     | •   |     |     |     |    |   |   |   | 480 |

|     | CLIP   | 4           | •     | •      | •   | •   | •   |     | •   | •    | •   |    |      |     |     |   |     |     |     | •   |     | •  | _ | • |   | 482 |

|     | Mass   | ive         | ely   | P      | ara | al  | le  | 1   | Pr  | :00  | ces | SS | or   | _   |     |   | •   | •   |     | •   | •   | •  | • | • | Ĭ | 485 |

|     | MIT    | Con         | ne    | ct     | ioi | n i | Mad | ch  | ir  | ne i | _   |    | _    | •   | Ī   |   |     | Ī   | Ť   | •   | •   | ٠  | • | • | • | 489 |

|     | Othe   | rN          | lac   | hi     | 2   | Z   |     |     |     |      | •   | •  | •    | •   | •   | • | •   | •   | •   | •   | •   | •  | • | • | • | 401 |

|     | Summ   |             |       |        |     |     |     |     |     |      |     |    |      |     |     |   |     |     |     |     |     |    |   |   |   |     |

|     | o unun | ацу         | ,     | •      | •   | •   | •   | •   |     | •    |     | _  |      | _   | _   | _ |     | _   | _   | _   |     | _  | _ | _ |   | 492 |

## LIST OF FIGURES

|     | •                                               |     |     |

|-----|-------------------------------------------------|-----|-----|

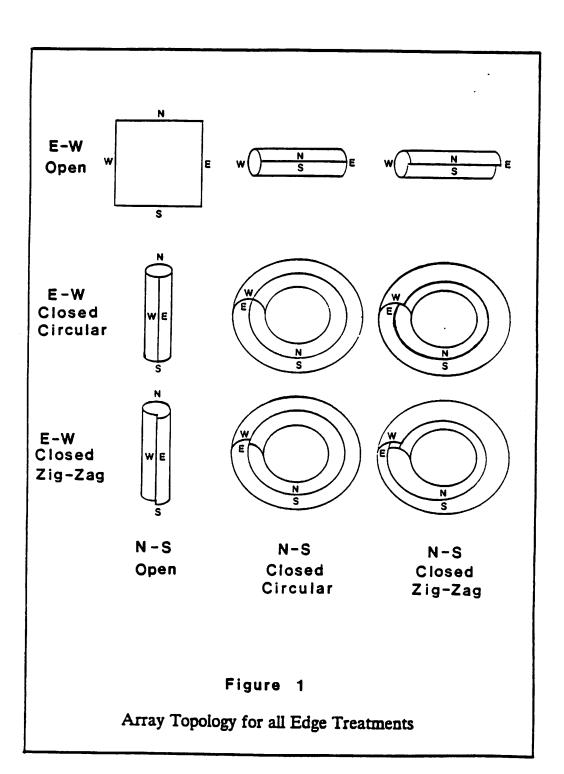

| 1.  |                                                 | •   | 96  |

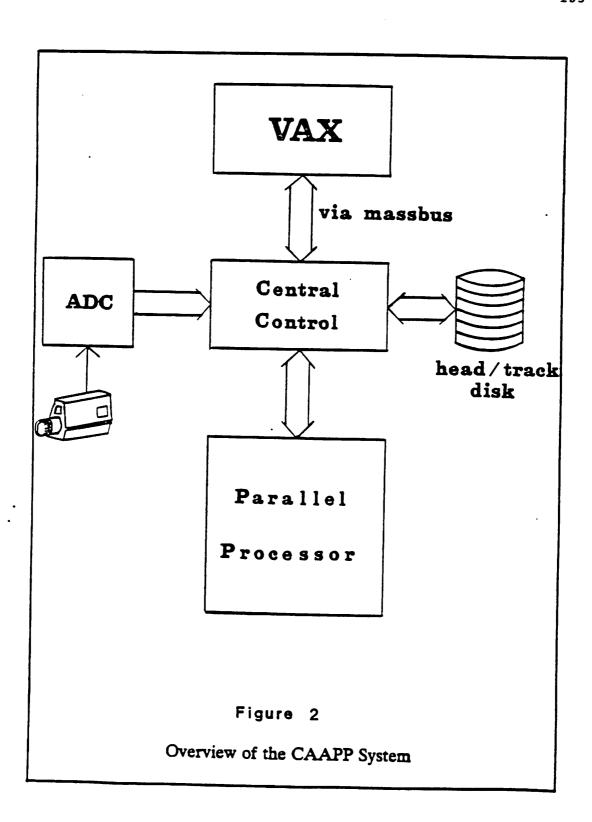

| 2.  |                                                 | •   | 103 |

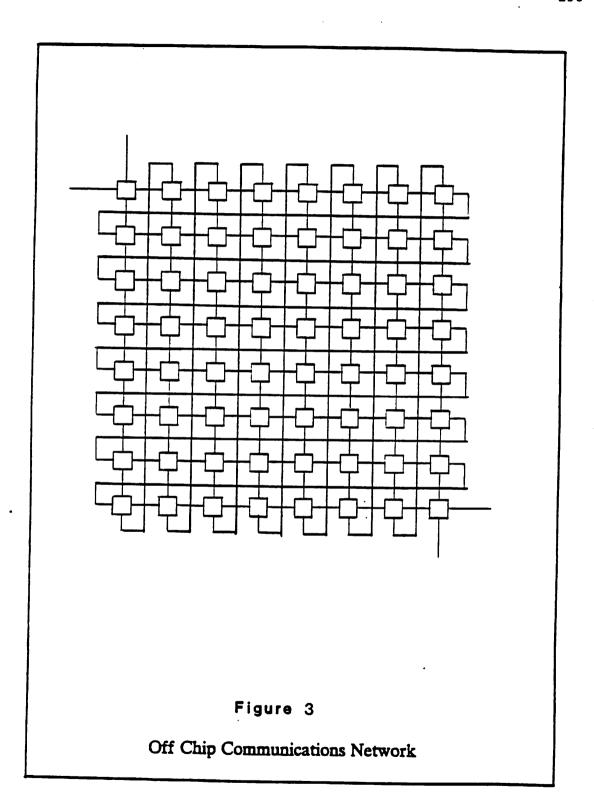

| 3.  | Off-Chip Communications Network                 | •   | 108 |

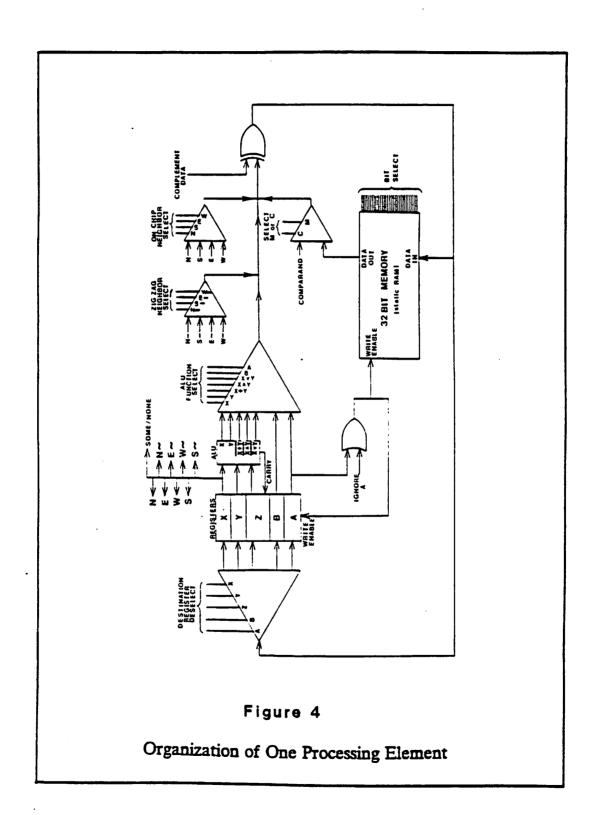

| 4.  | Organization of One Processing Element          | •   | 117 |

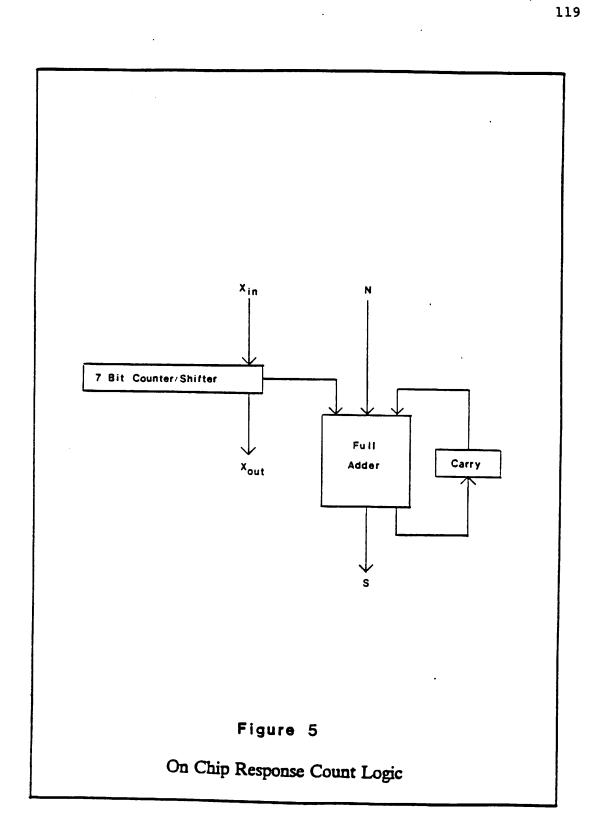

| 5.  | On-Chip Response Count Logic                    | •   | 119 |

| 6.  | CAAPP Chip Floorplan                            | •   | 137 |

| 7.  | Test Chip Floorplan                             | •   | 139 |

| 8.  | Processing Element Floorplan                    |     | 142 |

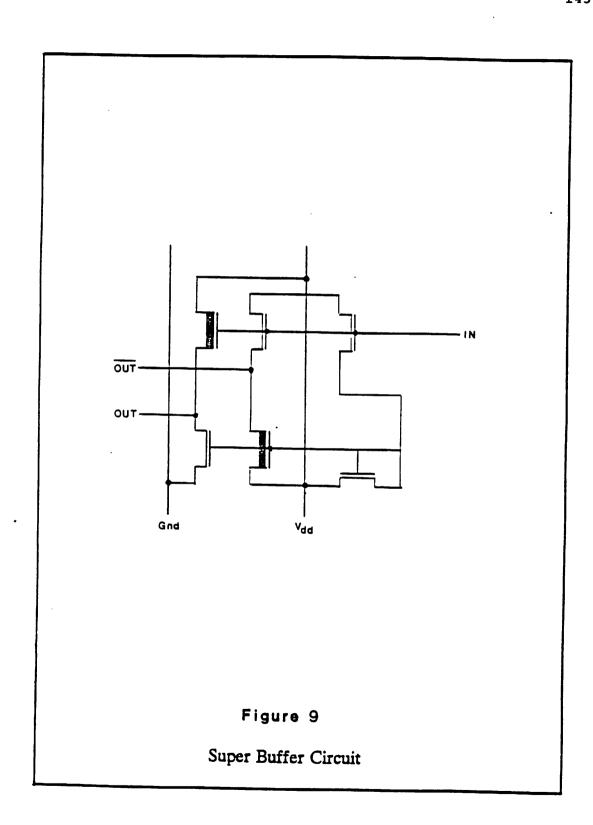

| 9.  | Super Buffer Circuit                            | •   | 145 |

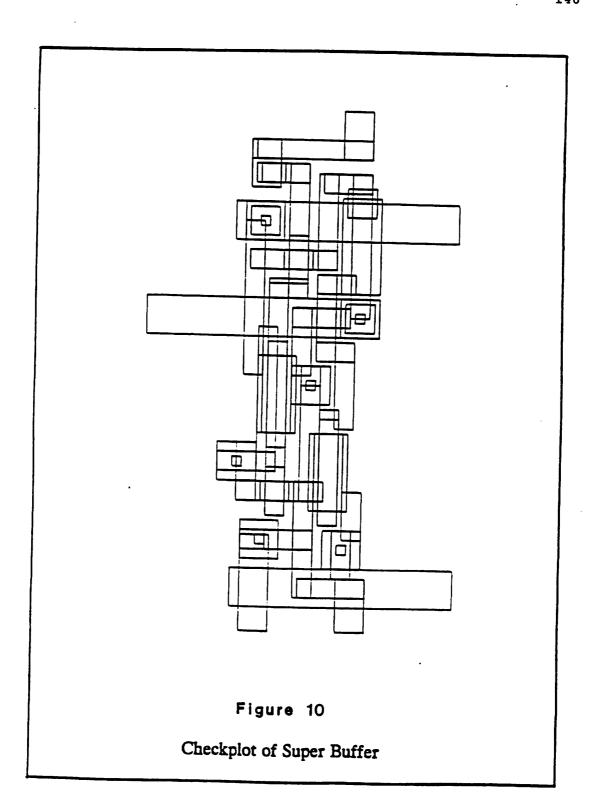

| 10. | Checkplot of Super Buffer                       |     | 146 |

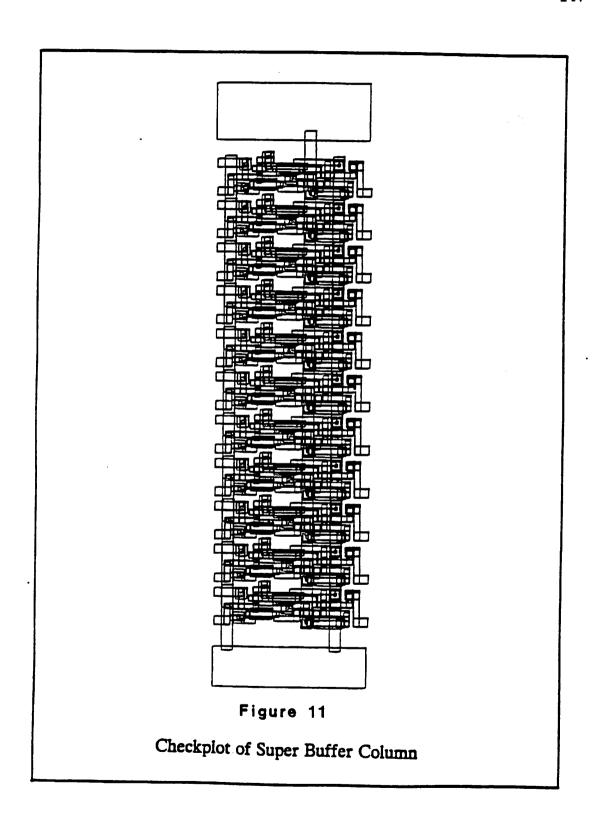

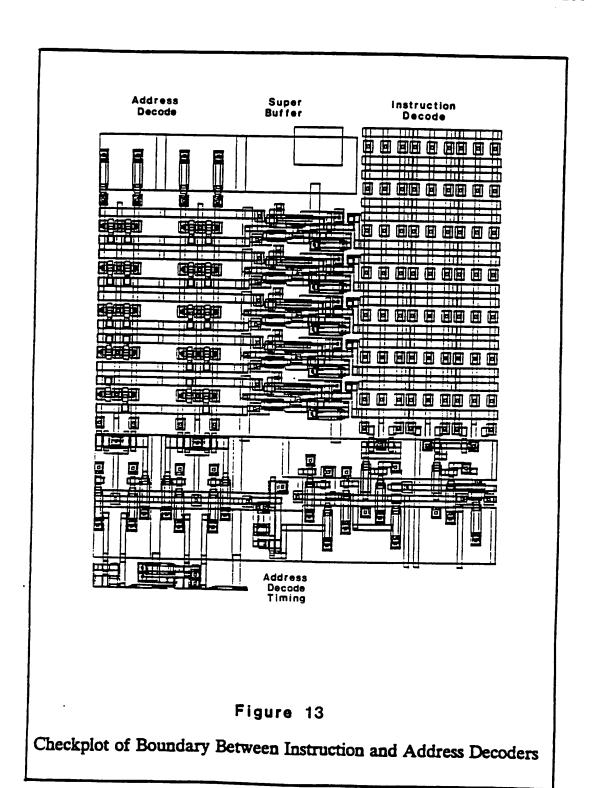

| 11. | Checkplot of Super Buffer Column                | •   | 147 |

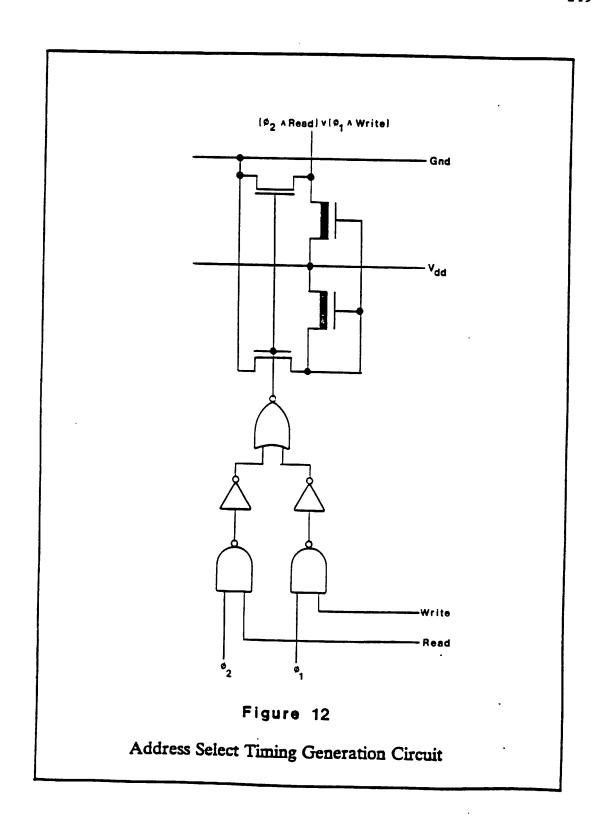

| 12. | Address Select Timing Generation Circuit        |     | 149 |

| 13. |                                                 |     |     |

|     | Address Decoders                                |     | 150 |

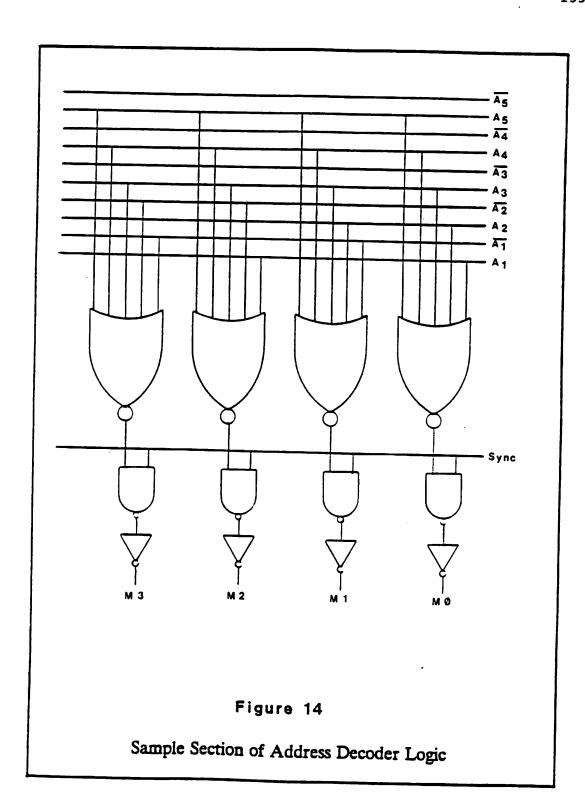

| 14. | Sample Section of Address Decoder Logic         | •   | 153 |

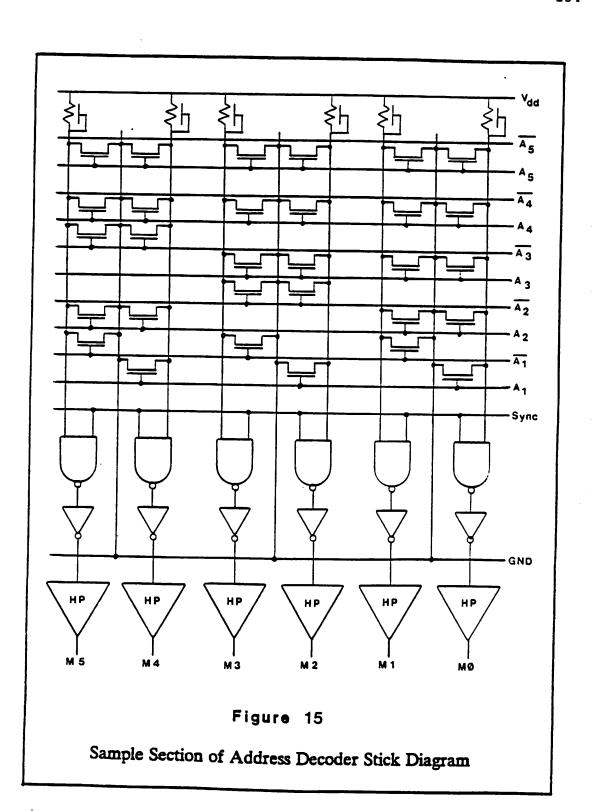

| 15. | Sample Section of Address Decoder Stick Diagram |     |     |

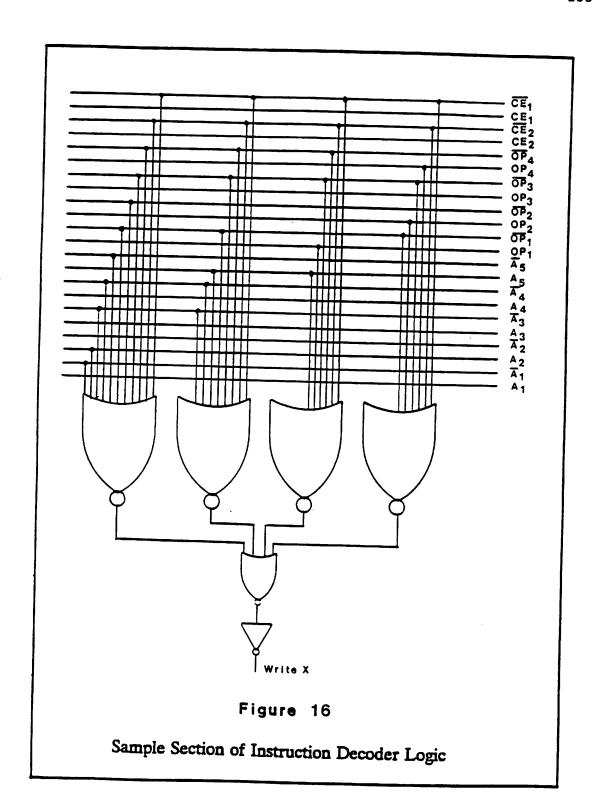

| 16. | Sample Section of Instruction Decoder Logic     |     |     |

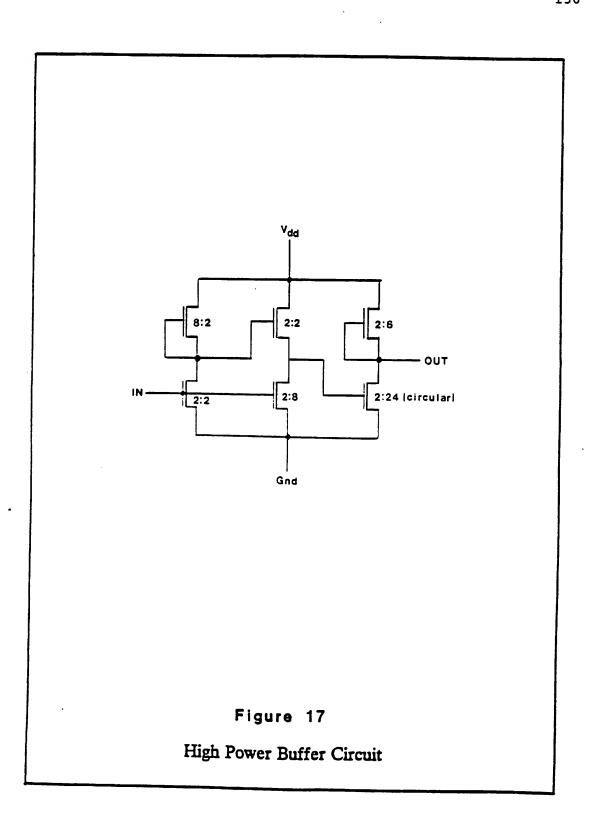

| 17. | High Power Buffer Circuit                       |     |     |

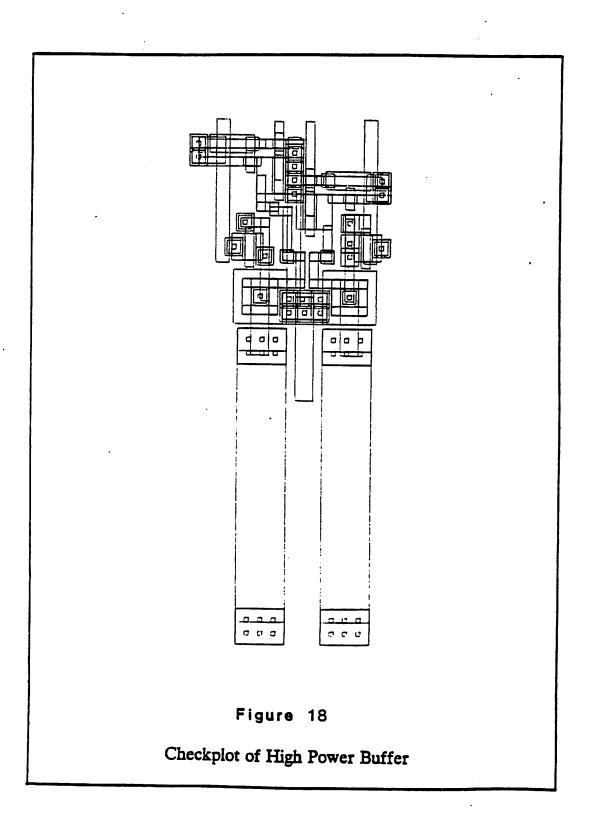

| 18. | Checkplot of High Power Buffer                  | •   | 150 |

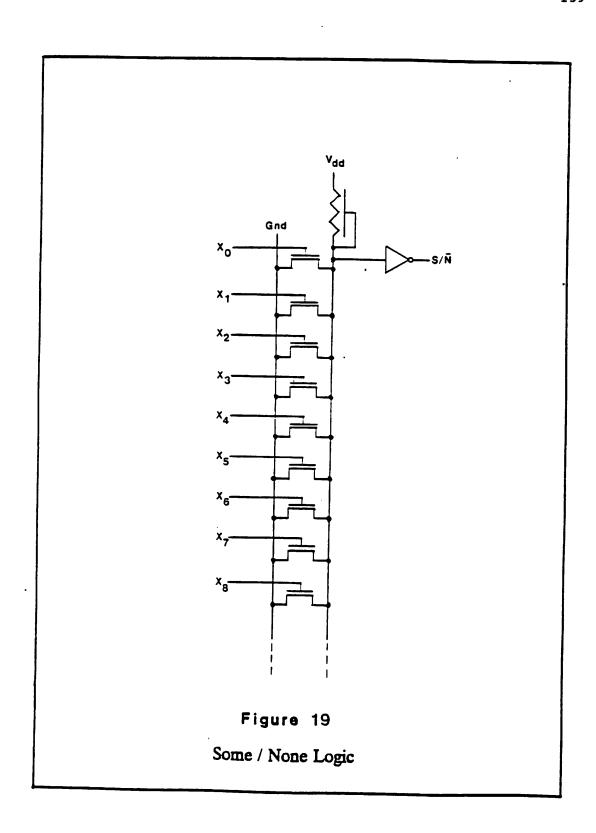

| 19. | Some/None Logic                                 |     |     |

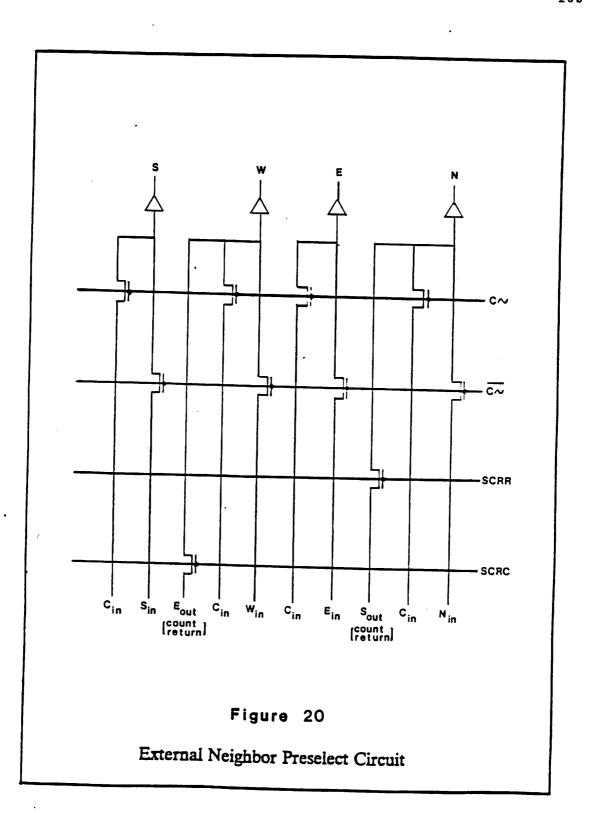

| 20. | External Neighbor Preselect Circuit             | . • | 100 |

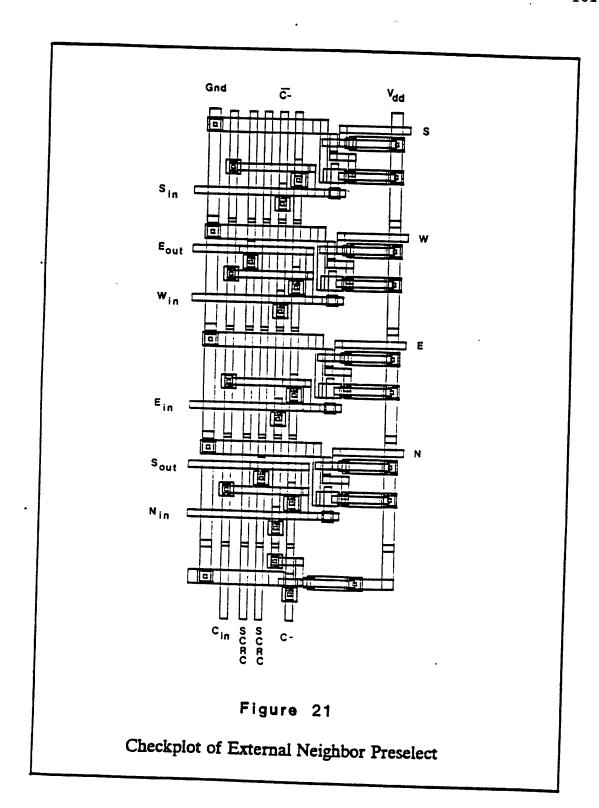

| 21. | Checkplot of External Neighbor Preselect        |     |     |

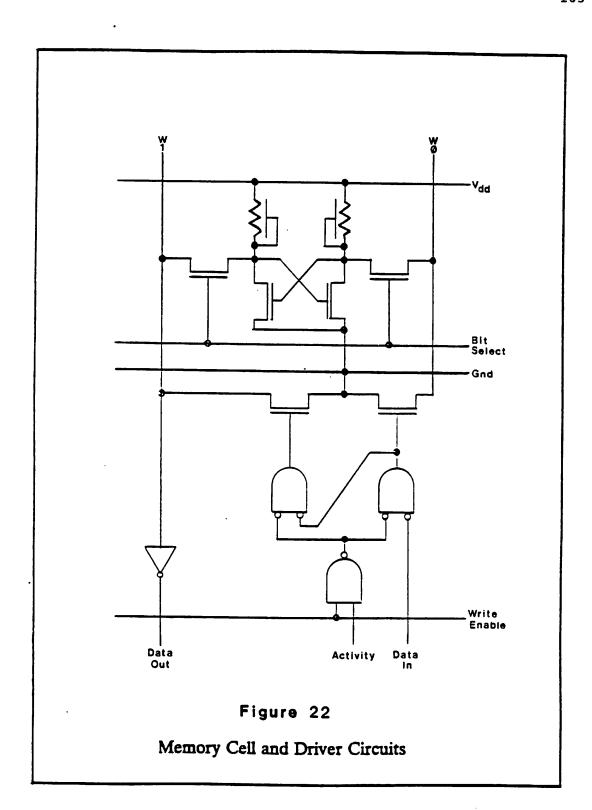

| 22. | Memory Cell and Driver Circuits                 |     |     |

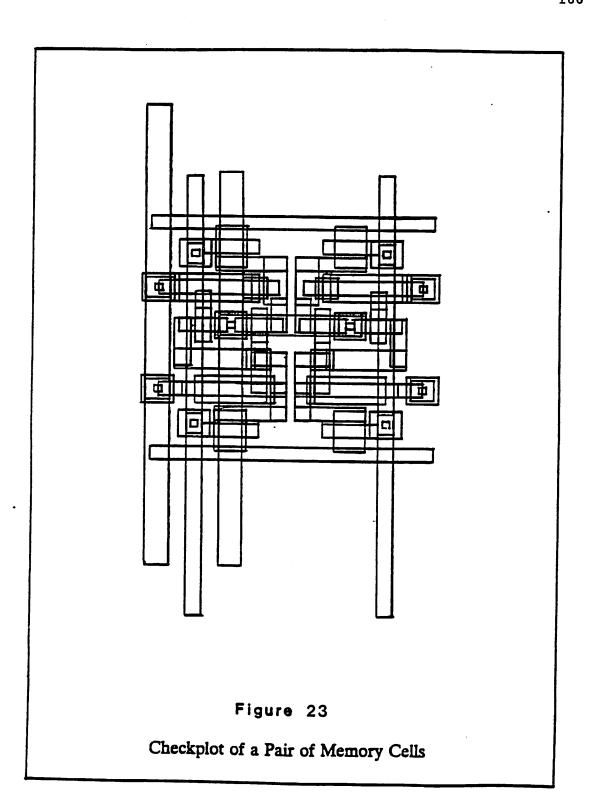

| 23. | Checkplot of a Pair of Memory Cells             | •   | 102 |

| 24. | Checkplot of a Pair of Memory Driver            | •   | 100 |

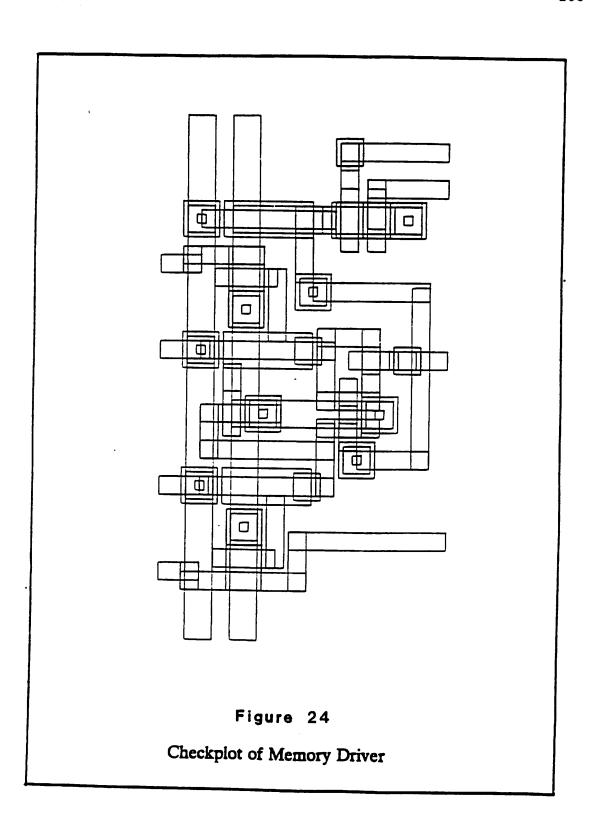

| 25. | Checkplot of Memory Driver                      | •   | 168 |

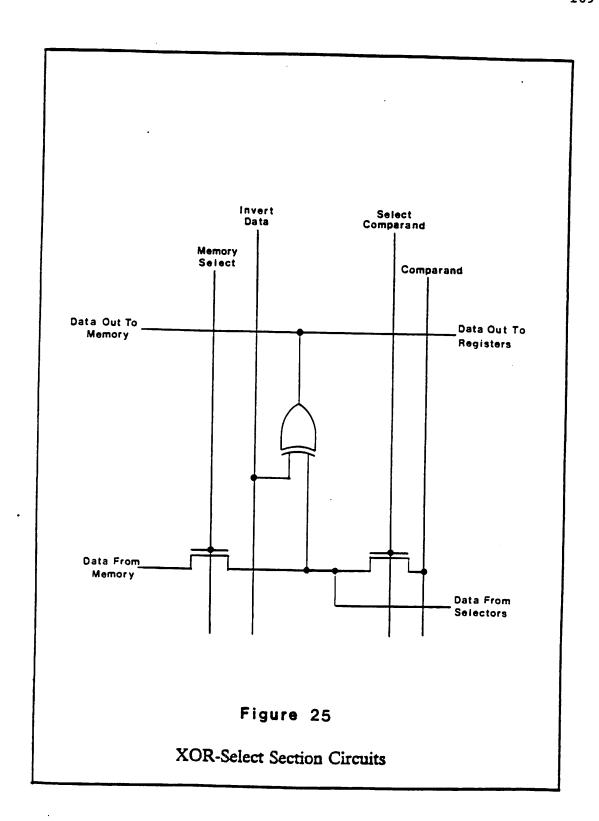

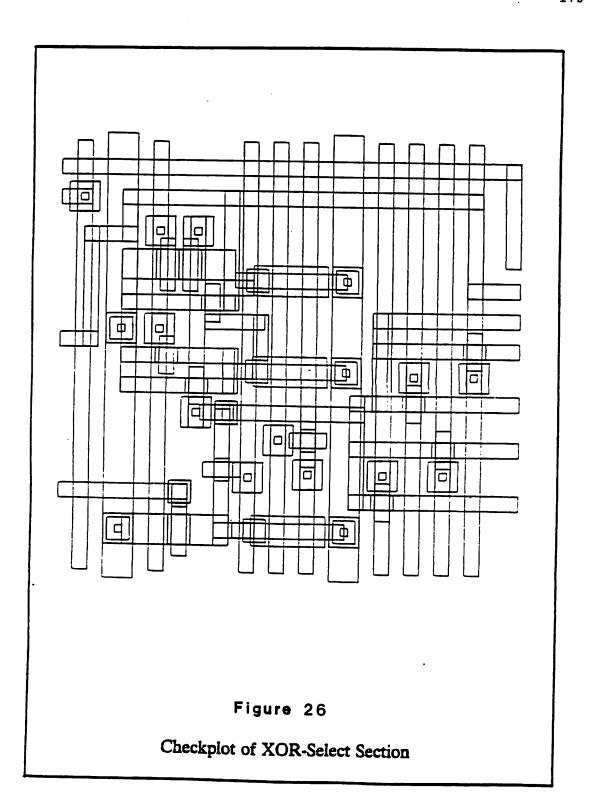

| 26. | XOR-Select Section Circuits                     | •   | 163 |

| 27. | Checkplot of XOR-Select Section                 | •   | 1/0 |

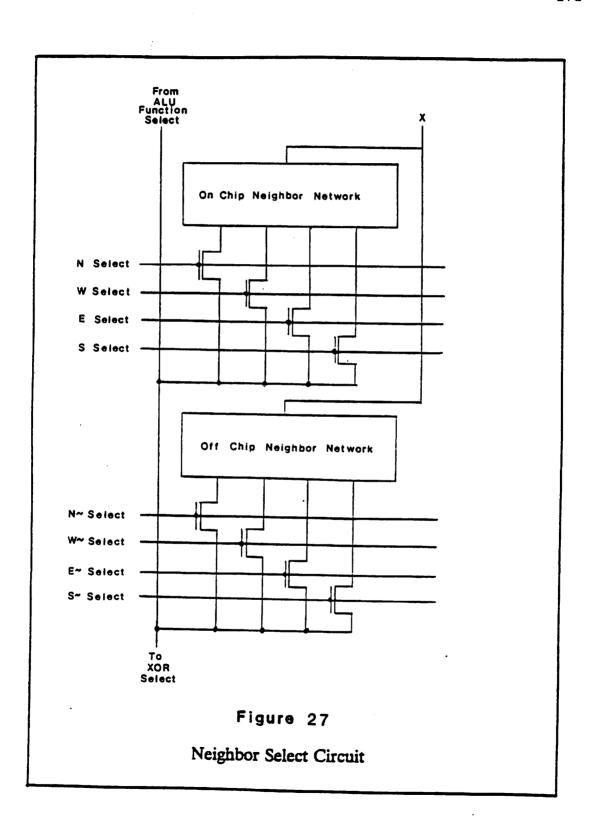

|     | Neighbor Select Circuit                         | •   | 172 |

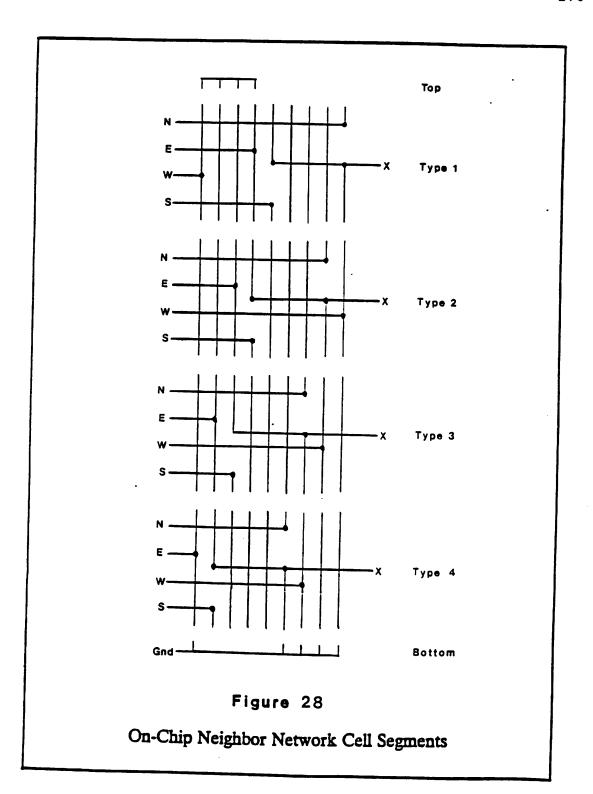

| 28. | On-Chip Neighbor Network Cell Segments          |     |     |

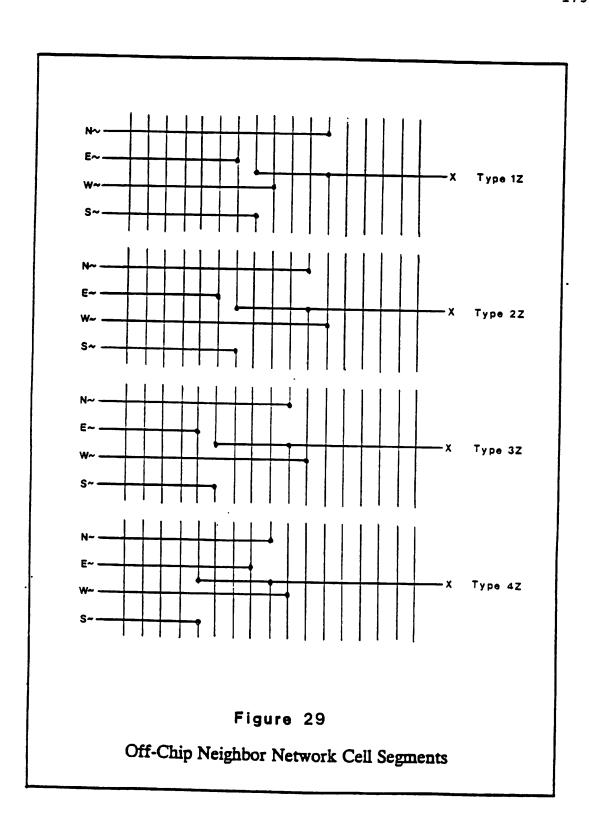

| 29. | Off-Chip Neighbor Network Cell Segments         | •   | 175 |

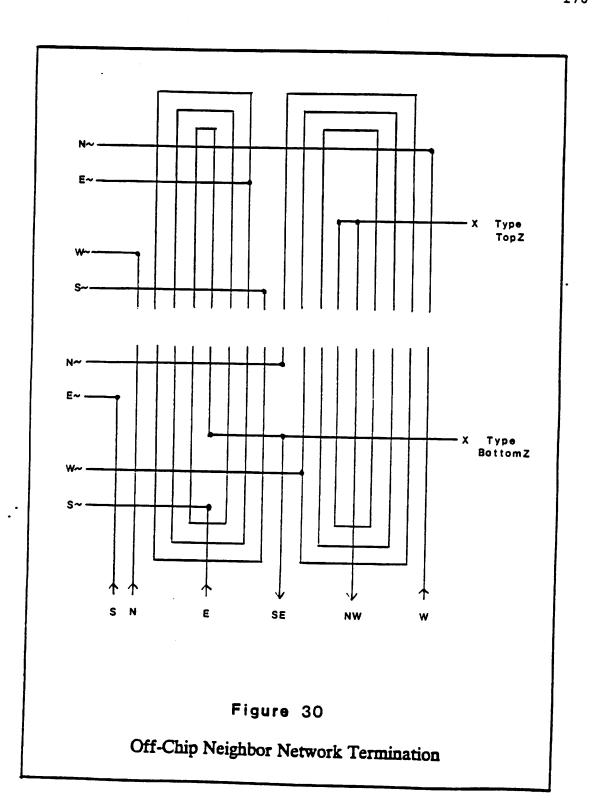

| 30. | Off-Chip Neighbor Network Termination           |     |     |

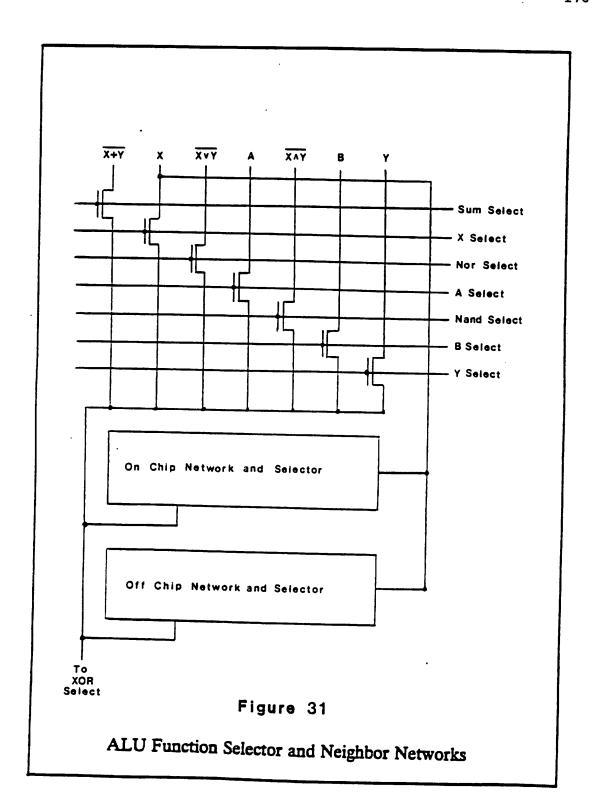

| 31. | ALU Function Selector and Neighbor Networks     |     |     |

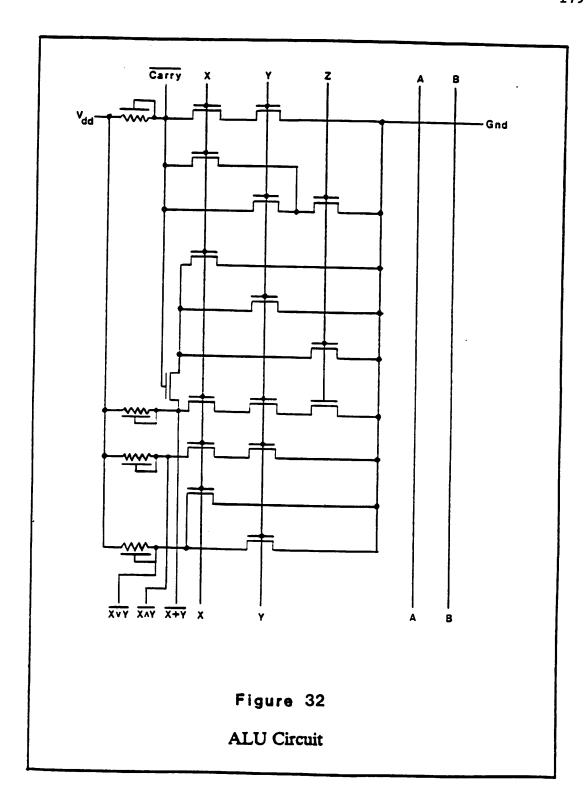

| 32. | ALU Circuit                                     | •   | 179 |

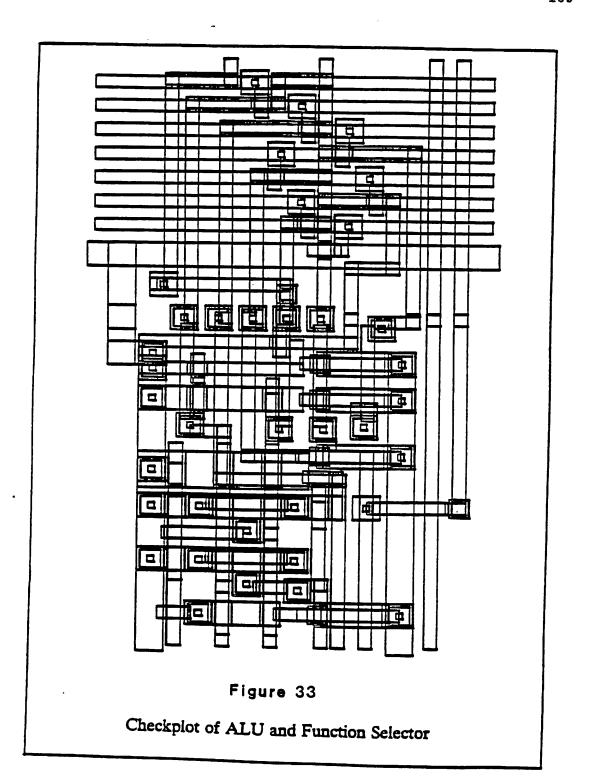

| 33. | Checkplot of ALU and Function Selector          | •   | 180 |

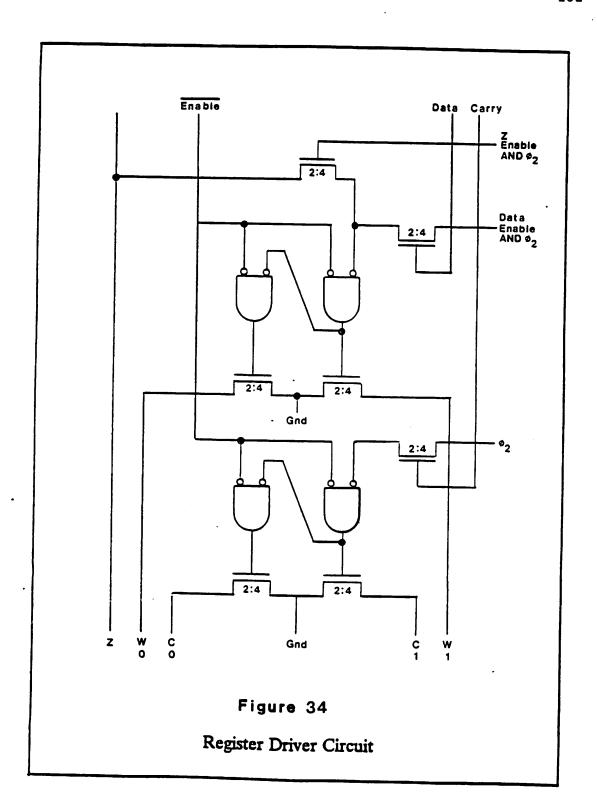

| 34. |                                                 | •   | 182 |

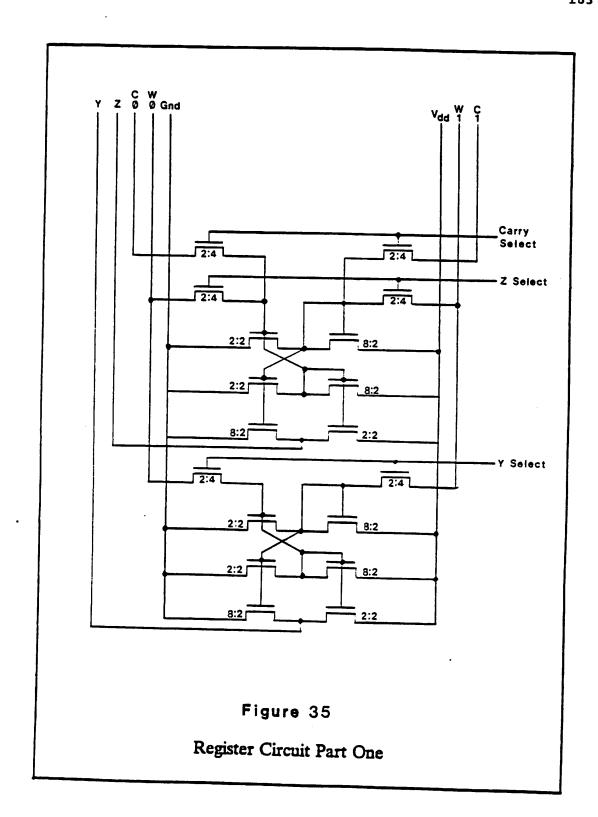

| 35. |                                                 | •   |     |

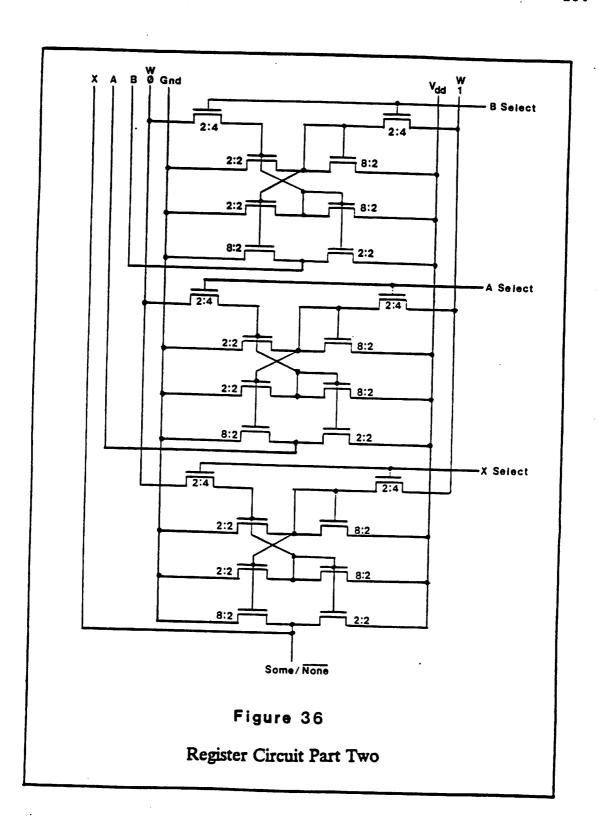

| 36. | Register Circuit Part Two                       | •   | 184 |

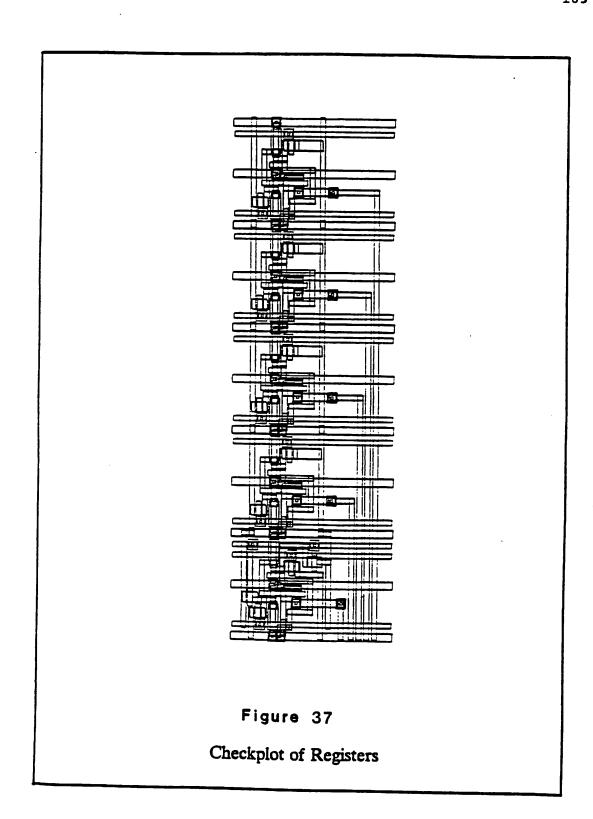

| 37. | Checkplot of Registers                          | •   | 185 |

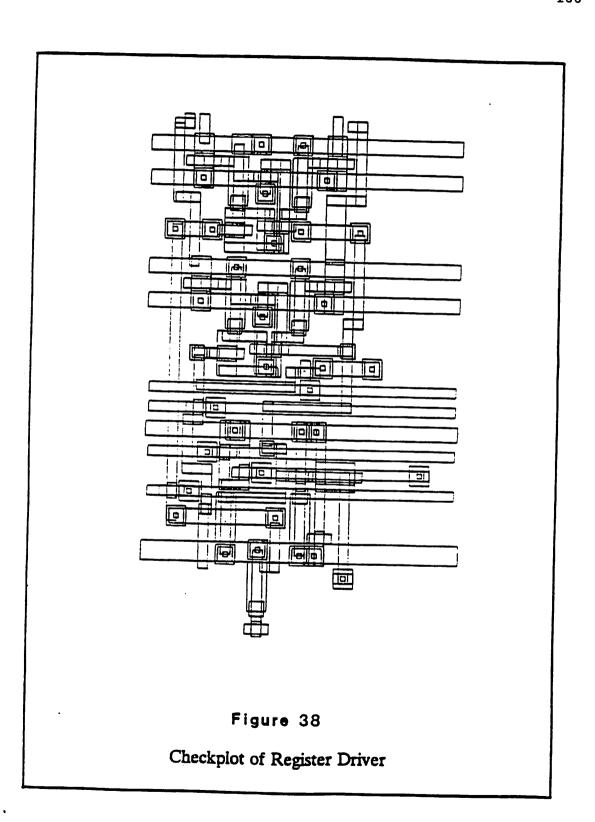

| 38. | Checkplot of Register Driver                    | •   | 186 |

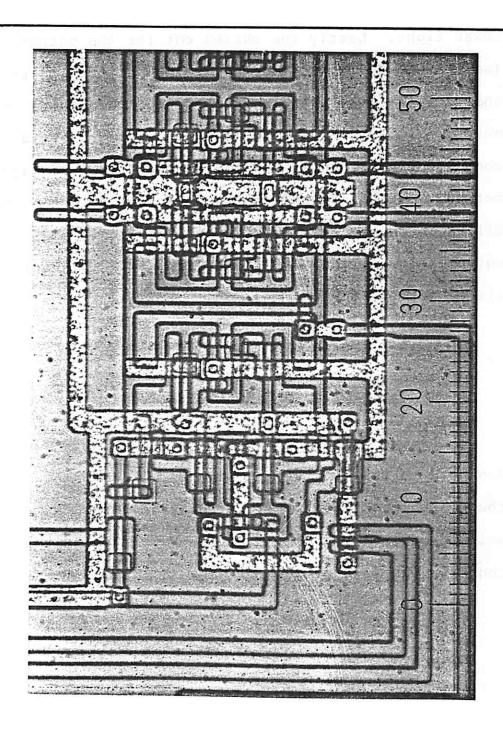

| 39. | Photomicrograph of Memory Cell and Driver from  |     |     |

|     | Test Fabrication                                | •   | 193 |

| 40. | Weight values for the Sobel Operation           | •   | 246 |

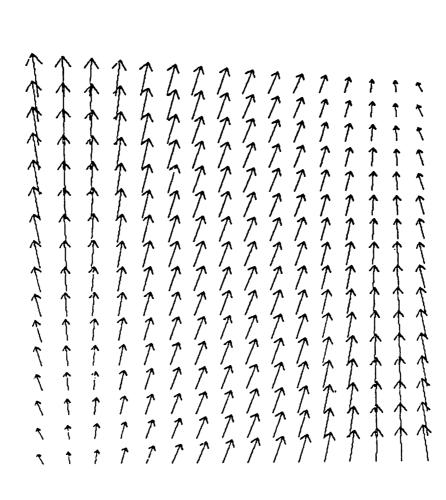

| 41. | Sample Flow Field                               |     | 276 |

| 12  | Difference Field for Comple Blow Bield          | •   | 277 |

| 43.        | Rotational Template Selected by the Algorithm      | 279 |

|------------|----------------------------------------------------|-----|

| 44.        | Translational Template Selected by the Algorithm . | 290 |

| 45.        | Sample Flow Field With Rotational Template         |     |

|            | Subtracted                                         | 281 |

| 46.        | Response to Poorly Matched Translation Template .  | 282 |

| 47.        | Translation Template Generating Example of         |     |

| 4.0        | Poor Response                                      | 283 |

| 48.        | Sample Flow Field With Random Spike Noise Added .  | 284 |

| 49.        | Difference Field for Sample Flow Field With Noise  | 285 |

| 50.        | Sample Noisy Flow Field With Rotational Template   |     |

|            | Subtracted                                         | 286 |

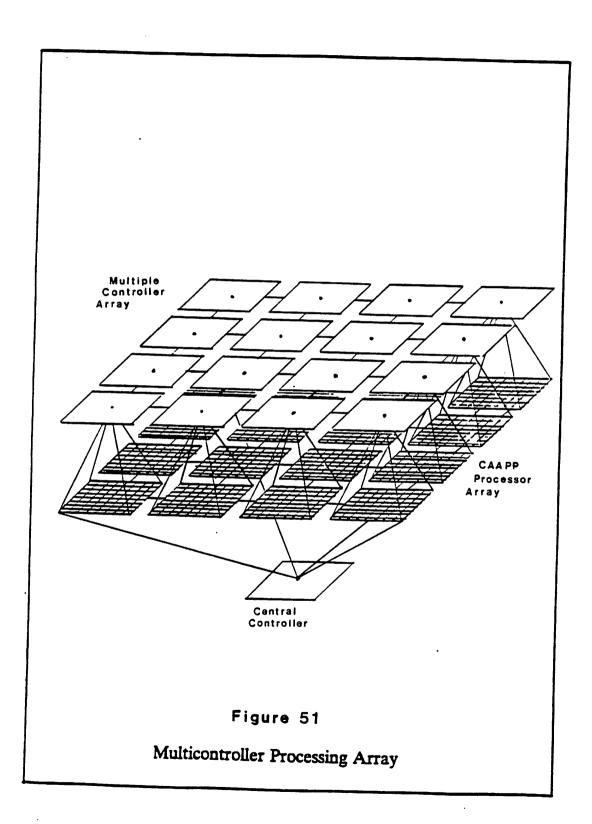

| 51.        | Multicontroller Processing Array                   | 361 |

| 52.        | Floorplan of Conservative Second Design Chip       | 371 |

| 53.        | Communication Network for Conservative Second      |     |

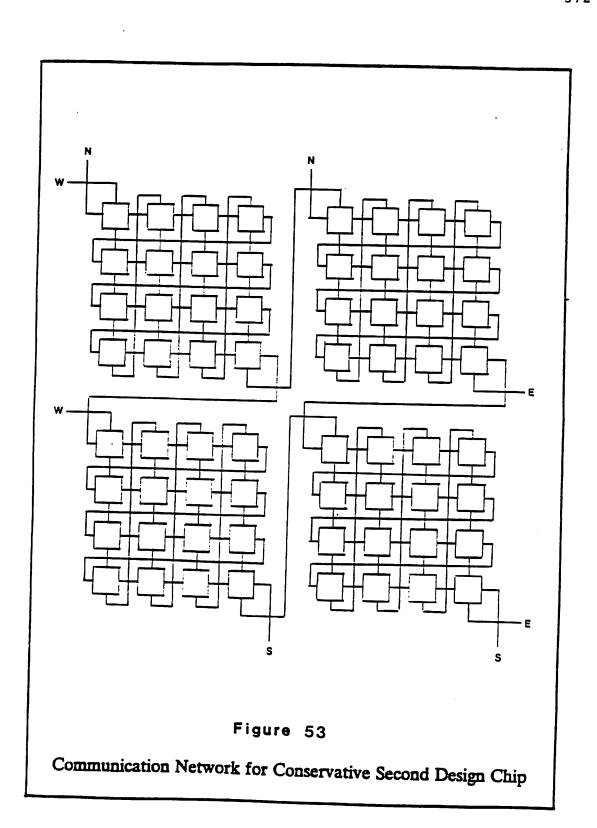

|            | Design Chip                                        | 372 |

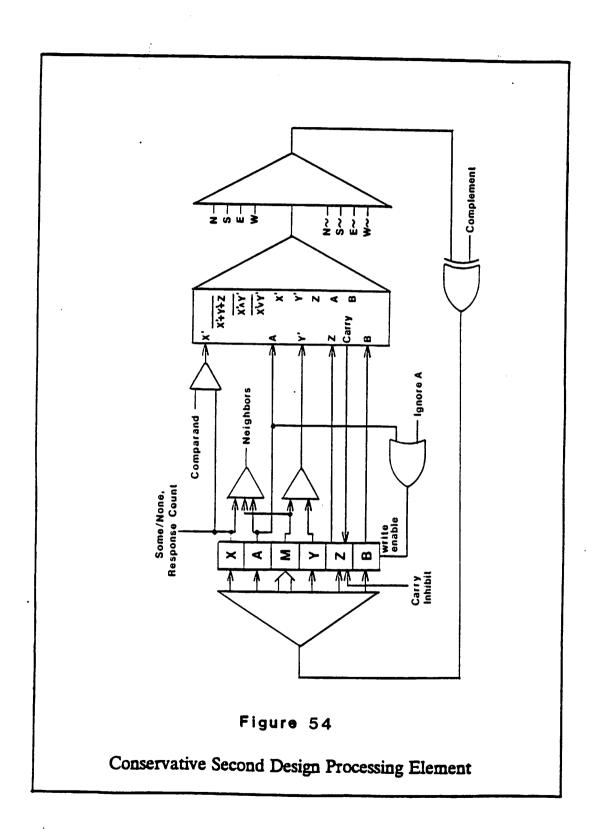

| 54.        | Conservative Second Design Processing Element      | 373 |

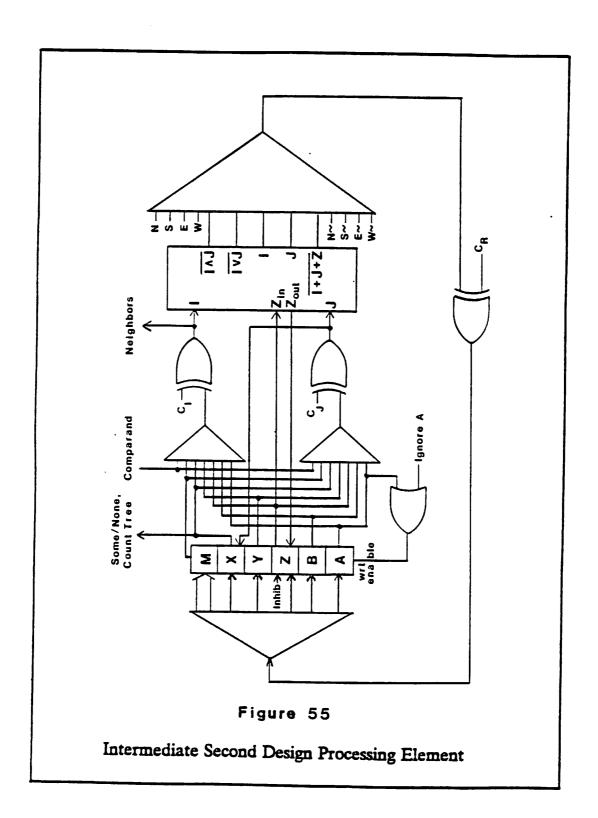

| 55.        | Intermediate Second Design Processing Element      | 207 |

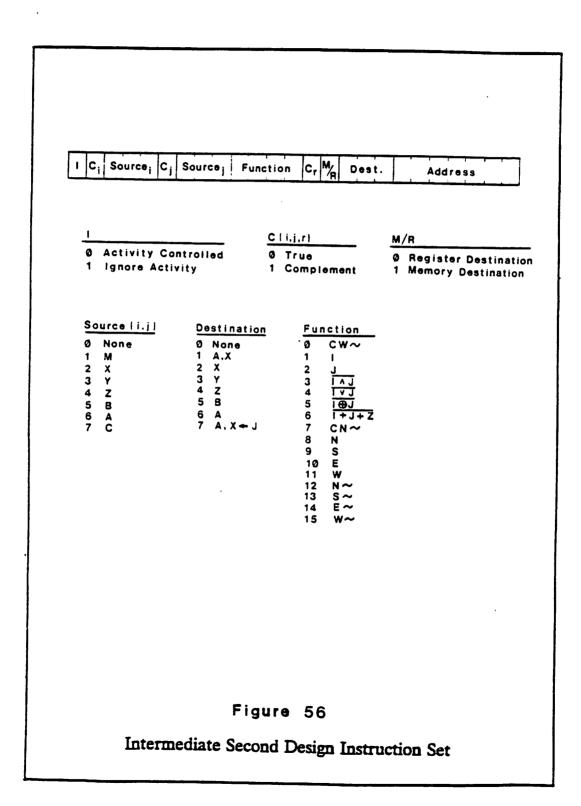

| 56.        | Intermediate Second Design Instruction Set         | 30/ |

| 57         | Intermediate Second Design Instruction Set         | 389 |

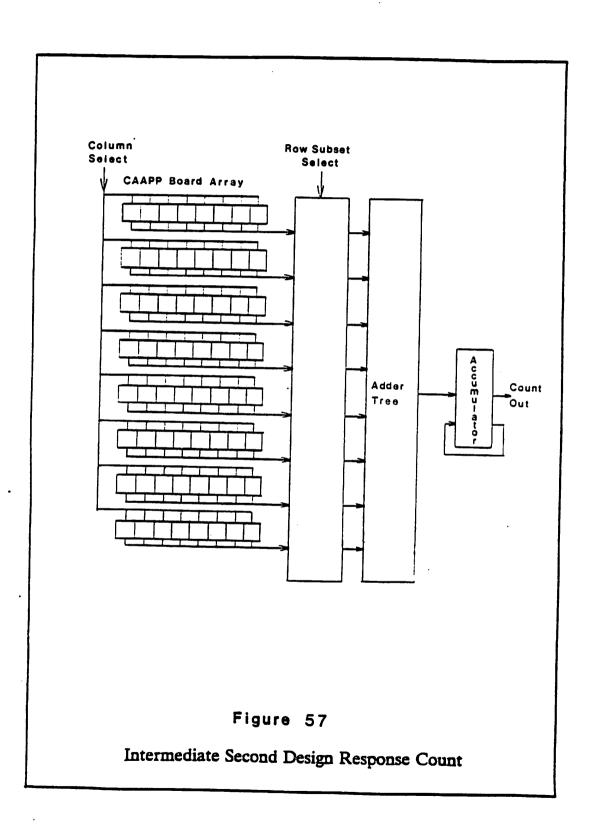

| J/.        | Intermediate Second Design Response Count          | 390 |

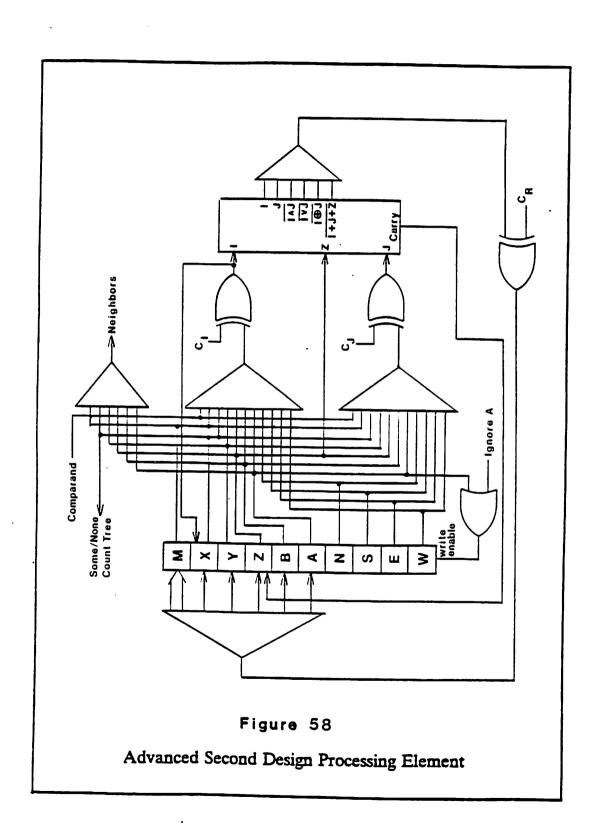

| <b>58.</b> | Advanced Second Design Processing Element          | 401 |

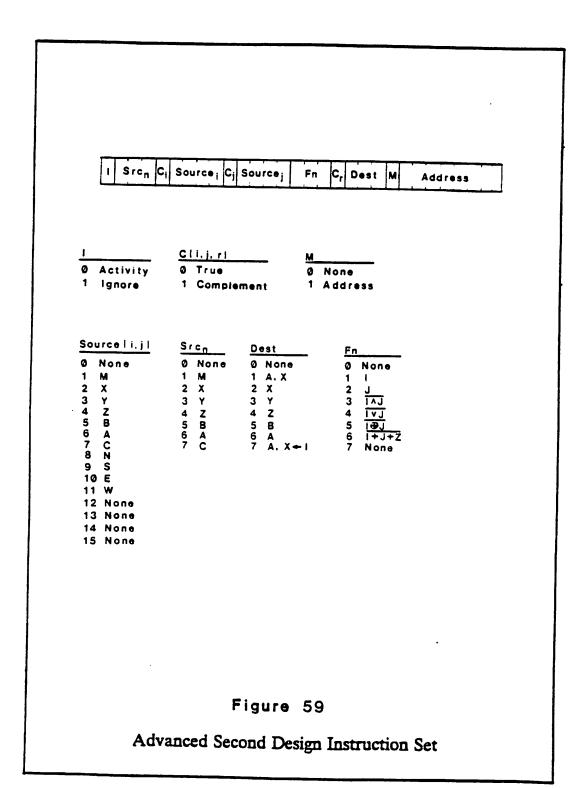

| 59.        | Advanced Second Design Instruction Set             | 403 |

## LIST OF TABLES

| 1.  | Semionics REM Instruction Set                    |   | 50  |

|-----|--------------------------------------------------|---|-----|

| 2.  | Summary of Findings from REM Case Study          |   | 79  |

| 3.  | Summary of Design Constraints                    | _ | 87  |

| 4.  | Summary of Design Goals                          |   | aa  |

| 5.  | CAAPP Chip Instruction Set                       | • | 123 |

| 6.  | Circuit Board Connections                        | • | 133 |

| 7.  | CAAPP Chip Pin Assignments                       | • | 136 |

| 8.  | Instruction Decoder Patch Table                  | • | 151 |

| 9.  | Summary Statistics for Test Chip                 | • | 187 |

| 10. | Algorithms Developed for the CAAPP Evaluation .  | • | 106 |

| 11. | Instruction Occurrence Counts for Sample         | • | 190 |

|     | Algorithms                                       |   | 222 |

| 12. | Algorithm Count for Each Instruction             | • | 322 |

| 13. | Percent of Algorithms Using Each Instruction     | • | 323 |

| 11  | Average Number of Oggunners Bon Markett          | • | 324 |

| ) E | Average Number of Occurrences Per Algorithm      | • | 326 |

| 10. | Macro Usage Statistics                           | • | 365 |

| Τρ. | Enhancements Ranked by Speed Merit               | • | 366 |

| 17. | Conservative Second Design Instruction Set       | • | 376 |

| 18. | Pin List for Conservative Chip and Circuit       |   |     |

|     | Board I/O Lines                                  | • | 38Ø |

| 19. | Intermediate Chip Pin List                       |   | 394 |

| 20. | Intermediate Second Design Circuit Board         |   |     |

|     |                                                  |   | 396 |

| 21. | Advanced Chip Pin List                           | - | 405 |

| 22. | Advanced Second Design Circuit Board Connections | • | 406 |

|     |                                                  |   |     |

#### **Preface**

"Consensus is a necessary condition for a successful political system."

---Enid Bak

"Any system is characterized by action or behavior that is oriented toward specific goals."

---Talcott Parsons

High quality service at the front line has to start with a concept of service that starts with top management and finds its way into the structure and operation of the organization. The role of management is to build and maintain the culture, set expectations of quality, provide a motivating climate, furnish the necessary resources, help solve problems, remove obstacles and make sure high-quality job performance pays off.

#### CHAPTER I

## INTRODUCTION AND OVERVIEW

"And generally it is good to commit the beginnings of all great actions to Argus with his hundred eyes, and the ends to Briareus with his hundred hands; first to watch and then to speed..." -- Francis Bacon: Of Delays

The focus of this dissertation is the design of a highly parallel computer architecture for image processing and computer vision. There are three basic problem areas that must be integrated in order to produce an effective machine design. These three areas are: Computer vision, computer architecture and engineering. From the computer vision area it is necessary to determine what is required of a machine that can be used to facilitate the solution of the vision problem. From the computer architecture area it must determined what machine structures should be selected meet the requirements set forth by the vision area. engineering problems that must be addressed are the limitations of current fabrication technology, and what can actually be built within those limitations. This involves not only VLSI circuit design, but also integrated circuit packaging technology, circuit board fabrication technology, power and signal distribution techniques, heat dissipation problems, radio frequency electrical shielding, circuit board and integrated circuit connector technology, and even mechanical mounting technology for housing the completed system.

#### The Vision Problem

Returning to the first of the problem areas, computer vision, a close examination will reveal that specifying the simple task. The processing requirements is not а difficulty is that the computer vision problem itself is far from being solved, and is currently a rapidly evolving area of research. At this point in time, nobody can give a detailed algorithmic specification for a general vision Rather than a set of specific interpretation system. processing requirements, then, it is only possible to give a list of general features that must be present in any machine that is to be used to significantly advance the problem. It is believed that if such machines are they will greatly facilitate research and define many issues in machine vision development.

In the discussions that follow, there will be little direct reference to image processing which, usually, refers to the enhancement and classification of images. In general, the computer vision problem subsumes the tasks

performed in normal image processing. The computer vision problem can be summarized as the automatic transformation of an image to a symbolic form that represents a description and an understanding of the content of the image. This process may be referred to as an iconic to symbolic transformation.

From our perspective, the computer vision problem will be described as involving three levels of processing. are referred to as the low, intermediate and high levels. The low level consists mainly of operations on pixels and neighborhoods of pixels, similar to the types of operations in standard image processing tasks. The intermediate level provides an interface between the low and high levels of representation, that is, between an iconic pixel-based representation and the symbolic elements representing visual knowledge. In the UMASS VISIONS system 85], which is the environment in which most of this research was conducted, the intermediate level consists of a symbolic description of the two dimensional image in terms of regions and line segments, and their associated attributes. In some systems this level would consist representations of surfaces, or more generally, "intrinsic" features of the physical environment that registration with the image.

high level processing relates the symbolic two-dimensional representations of the intermediate level to object descriptions, stored in а knowledge base of information about the three-dimensional world. The result is a symbollic representation of the content of a specific image in terms of the general stored knowledge of the object classes and the physical environment. Communication between these levels is by no means unidirectional. In most cases, recognition of an object or part of a scene at the level will establish a strategy for further processing and probing at the low and intermediate levels, in order to pull out additional features under the guidance of a partial interpretation.

Based on this general view of the vision problem, a key requirement is a flow of communication and control both and down through all levels of visual representation. the upward direction, the communication consists of summary information and statistics that allow processes at levels to evaluate the success of lower level operations, and also the passing of actual symbols. downward direction the communication consists of commands for selecting subsets of the image for specifying further processing in particular portions of the image, and requests for information in terms of the intermediate representation.

The long range goal, of course, is for all of this to be done in "real time". Real time can best be defined as whatever time the processing may take without causing the system to fail to meet its time dependent goals. By this definition, real time is purely application dependent. example, vehicle navigation in a dynamic environment requires control decisions to be made roughly once each second. This, however, depends upon the speed of vehicle and the speeds of independently moving objects in the environment. If the vehicle is being visually guided, then several frames may need to be processed in one second in order to determine parameters of motion. Therefore, many of the low level operations necessary to achieve this must be performed at video rate. Specifically, the time for scanning one video frame (one thirtieth of a second) will be used as a basis for speed comparisons. It should be noted that this was simply chosen as a convenient time period for discussion and comparison of operating speeds in relation to Many applications will, as mentioned above, not real time. impose such strong time restrictions.

It is obvious that many applications require some form of massive parallel processing. Consider a serial machine, with a one microsecond instruction time, processing a 512 by

512 image (roughly a quarter of a million pixels). Even if an image operation can be performed in 20 instructions each pixel, the total time will be five seconds for operation. Vision processing might require hundreds of such operations, so it is quite obvious that a serial processor will take too long to generate a result even for application that requires far less than video rate processing. This is due to the well known "von Neumann bottleneck", in which a large memory must be accessed and processed one cell at a time.

From the above description of the computer vision problem, a set of general requirements for a computer vision architecture can be deduced. Not the least of these is the ability to process images in real time, preferrably with a series of many operations being performed in a frame time. As a separate point, this implies that the machine must be able to load (and possibly dump) a complete image in well less than a frame time (or in parallel with the actual processing of a previous frame). Loading a 512 by 512 by 16 bit image in under one frame time represents a rather high data transfer rate. Since a great number of low level operations will be needed to support processing at the higher levels, the speed requirement would tend to indicate the need for a pixel per element class, mesh connected

cellular array processor. It is generally recognized that these provide the greatest speed in performing low level image operations.

Most important of the architectural requirements, however, is that a general vision machine should provide mechanisms for communicating information and control both up and down through the three levels of representation. The machine must be able to provide the necessary summary information quickly, so that it can try a variety of processing approaches to produce the best results. This type of communication will be necessary to permit the autonomous transformation of an image to a set of meaningful symbols. For this reason, the mechanisms that provide the summary information must be applicable to both pixel and symbol data.

A key issue in achieving an effective architecture, is the ability to maintain the low and intermediate representations, pixels and symbolic region, line and surface representations simultaneously in the same machine. The necessity of dumping an image out, for evaluation by a sequential program, must be avoided at all cost. It is simply too time consuming to transfer the volume of information contained in an image. Even if it took no time to dump the information, the time required for serial

evaluation would still be too great. Dumping an image for outside evaluation simply defeats the entire purpose of having a special parallel processor for computer vision. Instead, the computer vision machine must be able to provide enough feedback to the controlling processor to allow all of the operations to take place within the vision machine itself.

## The Architecture Problem

The problem facing the computer architect is to design a machine that is specialized for vision processing but which is sufficiently general that new approaches, to the various aspects of vision, can be implemented on it. It is quite simple to build special purpose machines that implement particular image processing algorithms with great speed. However, as mentioned above, computer vision research is a dynamic, rapidly changing area. New algorithms constantly under development and experimentation. stage of our understanding of the problem, for a vision architecture to be considered a contribution, it must sufficiently fast and general to allow experimentation up to the interpretation level.

The basic architectural issues to be addressed for

vision stem from the requirements of the problem: the ability to process both pixel and symbol data, a fast processing rate, the ability to select particular subsets of the pixels for special processing, feedback mechanisms that allow focussing of attention and data-directed processing (without having to dump the image for external evaluation), and the ability to transform an image into a set of meaningful symbols that describe it.

The general solution that we have developed and which will be presented in this dissertation is a machine that is a fusion of mesh connected cellular array processors and associative or content addressable parallel processing capabilities. The review chapter will more fully explain the benefits of combining these two sets of capabilities. briefly summarize, however, previous research has shown that a mesh connected cellular array is a structure that is extremely well suited to performing basic local processing tasks. With one processing element per pixel, such a machine can perform very quickly many of the basic image processing operations, including both the pixel and local neighborhood classes of operations. The problem with the cellular arrays that have been proposed is that generally do not provide for selective processing of pixel subsets (such as collections of regions or line segments

based on location or particular attributes of color, texture, size, shape, etc.), nor do they supply feedback to the controller. In other words, they do not provide the necessary bidirectional communication between symbolic processing and pixel processing. An image is simply loaded, some operations are applied to it, and then the image is returned for external sequential processing or human presentation.

Research on content addressable parallel processors (CAPP), on the other hand, has always emphasized selecting and processing arbitrary subsets of the data elements, providing feedback to the controller and doing whatever is necessary to keep from having to move data in and out of the processor. This is because the time required for loading the data, which is roughly equivalent to the time serially process the data with one operation, must included in the total processing time. In order to claim any significant speed increase over a serial processor, a CAPP must be able to average the data load time with a large number of parallel operations. One way of achieving this is reduce the number of times that the data to transferred in and out, by eliminating the need externally evaluate the results of processing. This can be done by providing global summary mechanisms that feed back

to the controlling processor, to allow it to perform the evaluation of the processing without removing the data from the processor. It will be seen that the combination of features provided by cellular arrays and associative processors is exactly what is dictated by the requirements of the vision problem. Thus, the end result of this particular bit of research is the design of a Content Addressable Array Parallel Processor (CAAPP) for computer vision.

The decision to build a computer vision machine based on a CAAPP architecture does not solve all of the architectural problems, however. It would be quite easy to build a CAAPP that is not well suited for vision. Therefore, determining the fundamental operations and processing element characteristics required to produce a good vision processor is the basis for much of the research that will be presented here.

## The Engineering Problem

This essentially boils down to: Given what is desirable in a vision machine, how much of it can actually be built. It would be desirable, for example, to give each CAAPP processing element the full power of a minicomputer.

Realistically, however, this simply isn't feasable in a processor per pixel machine. Besides the prohibitive cost, the complexity that such a design would entail will lead to very unreliable hardware.

The approach that has been taken, in the course of this research, has been to develop sets of constraints on designs which keep them within the limits of buildability for particular given technologies. The technologies involved integrated circuit fabrication are integrated circuit packaging, circuit board construction, connectors for wiring between circuit boards, backing storage, image displays, and so on. For all but one of the designs presented here, the technology employed is mature and reliable. The guiding philosophy has been that it both push the limits of architecture dangerous to technology at the same time. To do so is a sure formula for failure.

Thus, it is the engineering problems which will temper the potential solutions for the vision and architecture problems with realism. Throughout this dissertation the vision, architecture and engineering problems are continually being played off against each other to produce a good set of tradeoffs in the final design.

Some of the specific engineering problems that must be addressed are: number of componenents on a VLSI chip, heat dissipation, number of connections on chips and circuit boards, size of circuit boards, lengths of wires, signal propagation times, switching times, interfacing, power distribution, reliability, and cost. Proper evaluation of a design with respect to these can only be done through actual construction. Thus, it will be noted that part of this research involved actually designing VLSI chips to permit this evaluation to be done.

#### The Experience Problem

There is one more problem area which encompasses all of these three areas. This is the general lack of experience in designing real architectures for vision. Because no one has yet built a true, general vision machine, the initial foray into this realm is highly speculative. For this reason, the approach taken with this research has been to go through several iterations of design and evaluation in order to build a base of expertise on which the final conclusions can rest. This has included experimentation on, and evaluation of, an actual hardware system, as well as the use of several simulators.

### The Contributions of this Research

This research began by addressing the experience problem. Before designing a CAAPP system of our own, it was felt that the best course of action would be to spend months developing expertise by several programming previously existing CAPP system. In this case, a Semionics provided the hardware environment. The REM and results of our experience with it, as well as several local hardware modifications are described in chapter three. was this experience that heavily influenced the details of the design work that followed. Let us consider the important of the conclusions from this case study. The some/none and response count report mechanisms are very important because they provide a way for a controlling processor to quickly get a summary of the global state of the processing array. Specifically, some/none indicates whether any or none of the processing elements is in a given state, and the response count is an integer representing the number of processing elements in a given state. Other conclusions include the desirability of having processing elements with smaller memories in order increase parallelism, that nearest neighbor connections were valuable both because they allow certain types of algorithms to be performed and because, given smaller memories in the cells, they provide a means of simulating larger memories, and finally that bit serial processing elements are more cost effective than bit parallel elements.

From these findings an initial design for a CAAPP was developed. The machine was designed as a 512 by 512 array of processing elements, connected by a four way mesh, with hardware some/none, response count, and response resolution (the ability to select a single element for processing when several have responded to a query). Other global report mechanisms were developed in software, including maximum and minimum value, mean, standard deviation, and center of The response count mechanism is particularly innovative in that it is reasonably fast (about 1000 times faster than a serial count) but requires very little special hardware. This is because it takes advantage of the square grid communications network. The processing element design was kept very simple in order to enhance reliability, and consisted of five single bit registers, 32 bits of memory, a simple ALU and some data routing logic.

After designing the machine architecture, it was necessary to show that it could be built. This involved a VLSI design effort that resulted in a one-quarter size test chip with sixteen processing elements. (The eventual goal

was to put 64 processing elements on a single chip.) Although the chip was never fabricated, due to problems of obtaining access to the foundry for which it was designed, various electrical simulations indicate a high probability that it will work. This exercise also addressed the experience problem, giving us a good background in VLSI design, and a solid feel for what could and could not be done with mature fabrication technology. The first CAAPP design, the VLSI implementation of the test chip, and an analysis of the chip are presented in chapter four.

Besides showing that the first design could be cast in silicon and evaluated from a hardware viewpoint, it was decided that a software simulator should also be built that would allow various applications to be developed in order to also evaluate the architecture from a software viewpoint. Roughly 30 such applications were then programmed for the CAAPP, ranging from simple arithmetic macro operations to image enhancement processes. Each of these was evaluated for timing and instruction set usage. These are presented in chapter five. An algorithm for extracting rotational and translational motion parameters from an optic flow field is particularly interesting.

From the instruction set usage statistics an analysis of weak points, delays and bottlenecks in the architecture is

developed in chapter six. This chapter also presents a variety of solutions, forming a shopping list of potential hardware enhancements. The effectiveness of each of these enhancements is then evaluated by developing a figure of merit based on the speed increase that each would provide for a set of frequently used instruction sequences (weighted by frequency of use for each macro), versus a cost measure based on difficulty of implementation for each of the enhancements.

In the last part of chapter six, three sets of design constraints are presented to guide the design of three more advanced CAAPP architectures. One of these is identical to original set of constraints imposed on the first design. The resulting machine is in some sense the best that we could have done with the original design, given more experience. The second set of constraints is slightly relaxed to take into account three years of progress in what is considered mature technology. The resulting machine design represents what we would build now if given The third set of constraints is even further opportunity. relaxed to permit the use of the best available technology. The resulting design is probably impractical to build today, but may be buildable in a few years time. The set of enhancements chosen for inclusion in each design is based

upon the speed and cost evaluations discussed in the preceding paragraph. The result is a set of designs that are well tuned for three different levels of technological constraints, to best serve the needs of vision processing. Thus, the final result of this research is a CAAPP architecture that has been carefully tuned to serve as a general computer vision machine, providing the necessary processing power, communication paths, and control mechanisms to bridge the gap between the low, intermediate, and symbolic levels of image representation.

#### CHAPTER II

## A REVIEW OF ASSOCIATIVE AND PARALLEL PROCESSING

#### Introduction

This chapter presents the basic concepts of associative and parallel processing. It also examines some existing architectures in order to give the reader a feel for what is currently the state of the art. For readers that are interested, appendices A and B provide a broader presentation of the literature review from which this chapter is extracted.

The emphasis here will be oriented more towards associative processing than parallel processing because most people are more aware of the basic concepts of parallel processing than they are of associativity. The purpose of this chapter is to give the reader a feel for what each of these areas has to contribute to the vision problem. In general it will be seen that in associative processors what has been emphasized are control and feedback mechanisms, while parallel processors have tended to emphasize the topology of the communications network that links the processing elements. By combining the strengths of these two lines of research, a new architecture can be formed

which does a much better job of satisfying the needs of computer vision processing than either a pure associative machine or a pure parallel array machine.

It is also the purpose of this chapter to show how associativity can be used to perform in-cell operations that would require, on a typical parallel processor, special logic in each processing element. Thus, associativity can also be considered as a means of reducing the circuit complexity of processing elements without reducing their computational power. This is very important, since reducing circuit complexity will allow more processing elements to be built for a given cost, and therefore permit greater parallelism. Of course, simplified circuitry also enhances reliability.

## Definitions of Associativity

The glossary of the International Federation for Information Processing defines an "associative store" as: "a store whose registers are not identified by their name or position but by their content [64]." The glossary also gives a clarifying example in which it is noted that the retrieval of any item in such a store would be accomplished by performing a content search on all of its registers in

parallel with a single operation.

In a normal computer memory a pattern of bits, called the address, is presented to the memory. This activates logic circuits which "decode" the address and select one of the cells in the memory. Data bits can then be read from or written to that cell depending upon a control bit (usually called the read/write or R/W control line).

By contrast a Content Addressable Memory (CAM), sometimes called an Associative Memory, is accessed by broadcasting a data value to all of the cells in the memory. This activates logic in each of the cells which compares the data bits stored in the cell to the bit pattern being broadcast. If the values match, then the cell is selected. In a typical CAM, however, selecting a cell does not usually make it possible to read or write its contents.

## What CAM's are Used For

At this point, the logical question that arises is "What good is the ability to select a memory cell if you already know what's in it?" The answer lies in the other name for CAM: Associative Memory. A typical CAM cell is larger than a normal memory cell and is also divided into fields. The

fields contain "associated" pieces of data. The data that is broadcast to all of the CAM cells is compared against only a subset of these fields. Matches, however, select the entire cell. Thus the main use of a CAM is to search a list of records, by a key field, in order to extract associated data. In fact, CAMs are also referred to as "search memories".

The next question that is usually asked is "What good is having a record selected if you can't read or write the contents?" In fact it is possible to read the contents (and sometimes also to write into the cell) but not directly. The reason for this is based in the underlying nature of searching lists of data. The problem is that a list may contain more than one element with identical key fields. Because each cell in a CAM has its own comparison logic and selection status register (called the "response store"), all of the matching cells will be selected at once. This makes it impossible to then simply read the contents of the selected cells -- which one of the cells would the data value be taken from? Before the data can be read out, another operation must be performed to choose one of the selected cells. This is called the "find first" operation because it usually just selects the "first" of the selected data cells. The operation is also called "select first" and

is sometimes referred to as "response resolution". Once this is done, the cell's contents can be read. Of course, if only one cell is selected by the initial search, then its contents could be read directly. Determining the number of cells that have been selected is an operation that is often available in CAM systems.

Although many CAM's do provide a mechanism for counting the number of cells selected by a comparison, the operation is usually either very slow or, if fast, requires very expensive hardware. A less expensive alternative that almost all CAM's have is a single status bit that indicates whether any or none of the cells was selected. This usually called the some/none bit. It is most frequently used to test for completion of processing of all of the selected cells. This takes the form of a "while" loop that saves the response bits in a set of holding bits (called the "candidate" store), then finds the first responder, processes it, turns off the corresponding candidate bit and loads the remaining candidates back into the response store. The loop ends when the some/none bit indicates that there are no more responders -- all of them having been processed.

This essentially encompasses the basic features of a typical CAM. Almost every CAM ever designed has the

components and operations described above in one another as a part of it. The only detail yet to mentioned is the mechanism by which the subset of fields is selected for comparison. This depends upon the overall organization of the memory. The actual CAM memory cells may be either bit parallel or bit serial. In the bit parallel memory, every bit of every cell contains logic for comparing against broadcast bits as well as logic for combining results of the comparisons to set the response bits. serial memory, there is only one set of logic elements for comparison in each cell. The search value is then broadcast, one bit at a time, to the cells. As each bit is broadcast, the comparison logic in the cells checks that bit against the corresponding bit in the cells memory. result of all of the comparisons is accumulated so that if all of the bits match then the response store bit is set. In a bit parallel memory then, the fields are selected by storing a bit pattern in a register called the "mask" register. The mask is then broadcast along with the search value (which is often called the "comparand") and only the comparison logic for bits that are not masked is to produce a response value. In the bit serial memory, bits that are not to be included in the comparison are simply never fetched up by the comparison logic, and thus they do not contribute to the response value.

The reason for the two different memory organizations is Bit serial CAMs are much less expensive than bit parallel CAMs because the bit parallel CAM requires several times as many logic elements for the same number of storage The bit serial CAM can use standard memory elements with the addition of only one set of comparison logic for each memory cell. The bit parallel CAM must have a set of comparison logic elements for each bit of every memory cell plus logic for combining the results of all of the bit comparisons in each cell. The result is that if a bit parallel CAM has N bits in each memory cell, it will contain roughly N times as many logic elements as a bit serial CAM with the same number of cells. On the other hand, the bit serial CAM will be N times slower than the bit parallel CAM .for operations that can be applied to an entire field or cell at once. will see, however, that many Wе algorithms are inherently bit serial in nature. In the case of these operations, the bit parallel CAM has no advantage and may, in fact, be slightly slower than a bit serial CAM, due to the necessity of changing the mask for Even less expensive and still slower CAM operation. implementations exist in which the cells are processed serially as well. Such CAMs are no faster than general purpose computers but are useful as pre-prototype design

test beds in the development of parallel CAMs.

In summary, we can take a look at a list of the typical elements of an associative memory that was given by Minker [81] in his 1971 survey of papers on CAMs:

- 1) the memory array, which provides the data storage itself;

- 2) the comparand register, which contains the data to be compared against the contents of the memory array for searches; it may provide a shifting register for some input/output operations, and it can play an intermediate role in the transfer of data between the memory array and a general purpose computer, depending upon the configuration in which the processor is employed;

- 3) the mask register, which is used to contain data specifying portions of words for operations involving only word portions;

- 4) the resolver, which is used to determine the location of response bits in the response store;

- 5) the search logic, which causes the search commands received by the memory to be executed properly -- search operations are generally accomplished in a bit serial, word parallel fashion starting at the most significant bit; and

6) the response store, which receives vectors indicating which data satisfy a given search criterion and which can execute logical operations (such as shifting and Boolean operations on these vectors).

### A Database Search Example

To illustrate the use of CAM in a common area of application, we will examine an example of a database query system.

Suppose we have a database stored in a CAM that represents a catalog of astronomical objects. Each entry in the database will consist of the designation of the object, its type, subtype, celestial coordinates, distance, proper motion and system association. Not all of the fields will contain entries for all of the objects.

The simplest query would be to recall all of the information about a particular object. Because each object has a unique designation, we could simply broadcast the object's designation thus selecting the record that contains information pertaining to it and read it out directly.

Another query that we could make would be to ask the

designation of an object located at particular celestial coordinates. In this case we would broadcast values for two fields (right ascension and declination). Celestial coordinates do not always specify a unique object, however, so we will have to use a some/none bounded loop to read out all of the responders.

It is possible that the preceding query could give response. This would occur if the coordinates we broadcast were not quite accurate and thus gave a position in the sky where no object is present. We can solve this through the use of an inexact matching criterion. One simple way achieve this is to compare against just the high order bits of the stored numbers. By ignoring some of the low order bits, we reduce the exactitude of the matching operation and are thus checking a range of acceptable values. Doing this in the above example would essentially increase the size the "window" in space where we are searching for object. If the search fails again, the precision of comparison could be further reduced (increasing the size of the window) and another search performed. The process could then be repeated until an object is found.

Often we make conjunctive queries to databases. For example, we might ask for a list of all stars that have high proper motion and are either white dwarfs or K class stars

that are in binary systems. This is a fairly complex query but is easily handled in a CAM. First we set all of the response bits to one. Next we perform a set of queries, each of which will turn off response bits for cells that don't match but will leave the response bits for matching cells unchanged. In this case we would first query for all objects that are stars, then for all objects that have high proper motion. This would give us a list of all stars that have high proper motion. Next we store a copy of the response bits in the candidate store. Now we query for all white dwarfs, giving us a list of all white dwarf stars that have high proper motion. Then we exchange the candidate and response bits. Again we have a list of stars with high proper motion. To this list we apply the query for K class and then the query for membership in a binary system. now have a list of binary K class stars with high proper motion in the response store, and a list of white dwarf stars with high proper motion in the candidate store. last step uses some logic that we haven't discussed previously but which is usually present in CAMs candidate-response combinational logic. In addition operations for exchanging and copying values between candidate and response stores, operations are provided for combining the stores through logical AND and OR operations and for inverting, setting or clearing the bits

in either store. Thus the last step is to combine the two lists with a logical OR operation, putting the result in the response store; which gives us the desired list of records.