The Evaluation of Massively Parallel Array Architectures

Martin C. Herbordt

CMPSCI Technical Report 95-07

January, 1995

# THE EVALUATION OF MASSIVELY PARALLEL ARRAY ARCHITECTURES

A Dissertation Presented

by

MARTIN C. HERBORDT

Submitted to the Graduate School of the University of Massachusetts in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September, 1994

Department of Computer Science

© Copyright by Martin C. Herbordt 1994

All Rights Reserved

# THE EVALUATION OF MASSIVELY PARALLEL ARRAY ARCHITECTURES

A Dissertation Presented

by

MARTIN C. HERBORDT

| pproved as to style and content by: |   |  |  |  |  |  |

|-------------------------------------|---|--|--|--|--|--|

| Charles C. Weems, Chair             | _ |  |  |  |  |  |

| Allen R. Hanson, Member             |   |  |  |  |  |  |

| Donald W. Towsley, Member           | _ |  |  |  |  |  |

| Wayne P. Burleson, Member           | _ |  |  |  |  |  |

W. Richards Adrion, Department Chair Computer Science to the memory of my mother

#### ACKNOWLEDGMENTS

This dissertation would not have been possible without the help of many people. First, I would like to thank my committee for their many helpful comments and suggestions. Specifically, Al Hanson who taught me about computer vision, Wayne Burleson who taught me about VLSI, and Don Towsley who taught me about performance evaluation. Most especially, I'd like to thank my committee chair and my advisor and mentor for my entire graduate career, Chip Weems. Besides teaching me about architecture and writing, he suggested the final form of the topic, pulled me out of many blind alleys, and his vast store of knowledge was a constant help. Many other professors at UMass also contributed to my knowledge of computer science and so helped me with this dissertation. I would especially like to thank Arny Rosenberg who not only taught me theory but more importantly how and where to apply it, and Ed Riseman who's boundless energy and optimism serves as a model for all of us.

The first level of discussion and comments is always with the fellow graduate students in one's research group. In the IUA group I would like to thank Deepak Rana who gave me my first lessons in networks and parallel processor trade-offs, Mike Scudder who played the invaluable role of idea filter during the first part of the project, and Steve Dropsho who played that role during the latter stages. The IUA group has long benefited from its close ties with the VISIONS group. I have especially learned a great deal, not only about vision, but also about how to do research from Ross Beveridge, Bruce Draper, Bob Collins, Lance Williams, Teddy Kumar, and Harpreet Sawhney. I would also like to thank Scott Anderson, Jay Corbett, and Adele Howe for many useful discussions about thesis writing and research in general.

Jim Burrill deserves a paragraph all to himself: without his initial implementation of the class libraries for the IUA and his CAAPP simulator this work would have been impossible. It was also he, in my first days as a graduate student, who showed me the finer points of parallel programming and later answered some thousands of questions about compiler and architecture internals.

I've had many office-mates who have made life here pleasant, with whom I've discussed research, and from whom I've learned much about computer science. Those I haven't already mentioned in other contexts are Alan Boulanger and Glen Weaver. There are also many others at UMASS who helped provide sanity breaks, especially Gordon Kieffer and Frank Klassner. Our good friends Rob St. Amant and Luellen Brochu played that role outside of work.

Most of all I would like to thank my wife Ellen for her constant love and support. This is very much her dissertation as well.

#### ABSTRACT

#### THE EVALUATION OF MASSIVELY PARALLEL ARRAY ARCHITECTURES

SEPTEMBER, 1994

MARTIN C. HERBORDT, B.A., UNIVERSITY OF PENNSYLVANIA

M.S., University of Massachusetts Amherst

Ph.D., University of Massachusetts Amherst

Directed by: Professor Charles C. Weems

Although massively parallel arrays have been proposed since the 1950's and built since the 1960's, they have undergone very few systematic studies and these have covered only a small fraction of the design space. The major problems limiting previous studies are: computational cost of detailed and accurate simulations; programming cost of creating a test suite that compiles to the various target architectures and runs on them with comparable efficiency; and diversity of the architectural design space, especially communication networks. These issues are addressed in the construction of ENPASSANT, an evaluation environment for massively parallel array architectures that obtains performance measures of candidate designs with respect to real program executions.

We address the computational cost problem with a novel approach to trace-based simulation. Code is run on an abstract virtual machine to generate a coarse-grained trace, which is then refined through a series of transformations (a process we call trace compilation) wherein greater resolution is obtained with respect to the details of the target architecture. We have found this technique to be one to two orders of magnitude faster than detailed simulation, while still retaining much of the accuracy of the model. Furthermore, abstract machine traces must be regenerated for only a small fraction of the possible architectural parameter combinations. Using virtual machine emulation and trace compilation also addresses program portability by allowing the user to code in a single language with a single compiler, regardless of the target architecture. Fairness and programmability are obtained with architecture dependent application libraries for a small set of critical functions. The diverse design space is covered by using parameterized models of the architectural components which direct ENPASSANT in the evaluation of the target machines on the basis of user specifications.

ENPASSANT has already generated significant results, including effects of varying the number of dimensions in k-ary n-cubes, trade-offs in register and cache design, and usefulness of certain ALU features. Some surprising results are that bidirectional links provide a large advantage for k-ary n-cubes (where n=2) in an essential application, and that smaller rather than larger cache block sizes are favored for most applications studied.

# TABLE OF CONTENTS

|     |            | P                                                   | age      |

|-----|------------|-----------------------------------------------------|----------|

| Ac  | KNOW       | VLEDGMENTS                                          | v        |

| A   | STRAC      | CT                                                  | . vi     |

| Lis | ST OF      | Tables                                              | xii      |

|     |            | FIGURES                                             |          |

|     |            |                                                     | AIII     |

| CI  | HAPI       | TER.                                                |          |

| I   | In         | troduction and Background                           | 1        |

| 1.  | Intro      | ODUCTION                                            | 3        |

|     | 1.1<br>1.2 | The Problem                                         | 3<br>4   |

|     |            | 1.2.1 Computational Intractability                  | 4<br>5   |

|     | 1.3        | The Approach                                        | 7        |

|     |            | 1.3.1 The MPA Architecture Space                    | 8        |

|     |            | 1.3.4 Emulating Operators for Optional Features     |          |

|     |            | 1.3.7 Trace Compilation                             | 9<br>9   |

|     |            | 1.3.9 Virtual Processor Support                     | 10<br>11 |

|     | 1.4<br>1.5 | Outline of Results Achieved, Contributions          |          |

| 2.  | Mass       | SIVELY PARALLEL ARRAY EVALUATION: ISSUES AND REVIEW | 15       |

|     | 2.1        | General Issues in Architectural Evaluation          | 15       |

|     |            | <ul><li>2.1.1 Workload Approximation</li></ul>      | 16<br>16 |

|     | 2.2        | Techniques Used in Architectural Evaluation         | 17       |

|     |            | 2.2.1 Design From Requirements                      |          |

|    |            | 2.2.4<br>2.2.5<br>2.2.6 | Evaluation Using Representative Sub-Problems                                                                                                                           |

|----|------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |            |                         | 2.2.6.1       Complete Simulation       22         2.2.6.2       Trace-driven Simulation       22         2.2.6.3       Execution-Driven Simulation       23           |

|    | 2.3        | MPA 1                   | Evaluation: Issues and Previous Work                                                                                                                                   |

|    |            | 2.3.1<br>2.3.2<br>2.3.3 | Difficulties in MPA Evaluation         24           Benchmarks         25           Particular Evaluation Systems         26                                           |

|    |            |                         | 2.3.3.1       MAP Simulator       26         2.3.3.2       PAWS       26         2.3.3.3       SIMD Simulator Workbench       27         2.3.3.4       GT-RAW       27 |

|    |            | 2.3.4                   | Summary of Current Status                                                                                                                                              |

|    |            |                         |                                                                                                                                                                        |

| II | A          | rchit                   | ecture and Application Spaces 29                                                                                                                                       |

| 3. | Arch       |                         | RE SPACE: MASSIVELY PARALLEL ARRAYS                                                                                                                                    |

|    | 3.1        | Overal                  | l Organization 3                                                                                                                                                       |

| ÷. | 3.2        | Details                 | of Particular Components                                                                                                                                               |

|    |            | 3.2.1                   | PE Internals                                                                                                                                                           |

|    |            | 3.2.2<br>3.2.3          | Memory Hierarchy Design                                                                                                                                                |

|    |            | 3.2.4                   | InterPE Communication                                                                                                                                                  |

|    | 3.3<br>3.4 |                         | tudies                                                                                                                                                                 |

| 4. | APPL       | ICATIO                  | N SPACE: SPATIALLY MAPPED APPLICATIONS                                                                                                                                 |

|    | 4.1<br>4.2 |                         | Choose a Test Suite                                                                                                                                                    |

|    |            | 4.2.1<br>4.2.2          | Where MPAs Are Used                                                                                                                                                    |

|    |            |                         | 4.2.2.1 Computer Vision Paradigm                                                                                                                                       |

|    |            |                         | 4.2.2.3Computer Vision Tasks Suitable for MPAs424.2.2.4Low-level Vision Processing Applications434.2.2.5Low-level Vision Benchmarks on MPAs43                          |

|    | 4.3<br>4.4 | Chara                   | cterizing the MPA Workload                                                                                                                                             |

|    |            | 4.4.1                   | The ARPA Benchmark                                                                                                                                                     |

|    |            | 4.4.2                   | Correlation-based Correspondence                                                                                                                                       |

|    |            | 4.4.3                   | Weymouth-Overton Edge-Preserving Filter                                                                                                                                |

|    |            | 4.4.4                   | Region Merging Segmentation                                                                                                                                            |

|    |                                        | 4.4.5<br>4.4.6<br>4.4.7                                     | The Daumueller Line Finder                                                                                                                                                                                                                                                                            | 52                           |

|----|----------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|    | 4.5                                    | Chapt                                                       | er Summary                                                                                                                                                                                                                                                                                            |                              |

| II | I :                                    | Evalu                                                       | nating Massively Parallel Array Architectures                                                                                                                                                                                                                                                         | 55                           |

| 5. | ENP.                                   | ASSAN                                                       | NT: High-Level Overview                                                                                                                                                                                                                                                                               | . 57                         |

|    | 5.1<br>5.2                             |                                                             | eal Evaluation System                                                                                                                                                                                                                                                                                 |                              |

|    |                                        | 5.2.1<br>5.2.2                                              | Test Suite Issues                                                                                                                                                                                                                                                                                     |                              |

|    | 5.3<br>5.4                             |                                                             | Virtual Machine Methodology                                                                                                                                                                                                                                                                           |                              |

| 6. | Inpu                                   | T Cons                                                      | STRUCTOR SUBSYSTEM                                                                                                                                                                                                                                                                                    | . 64                         |

|    | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Overvi<br>Selecti<br>An Mi<br>Emula<br>Selecti              | iew                                                                                                                                                                                                                                                                                                   | 64<br>65<br>67<br>68         |

| 7. | Virt                                   |                                                             | ACHINE EMULATOR AND TRACE ANALYZER                                                                                                                                                                                                                                                                    |                              |

| •• | 7.1<br>7.2<br>7.3<br>7.4               | Proble<br>Virtua<br>Virtua                                  | ems with Trace-Driven Simulation                                                                                                                                                                                                                                                                      | . 72<br>. 74<br>. 76         |

|    |                                        | 7.4.1<br>7.4.2                                              | Correctness                                                                                                                                                                                                                                                                                           |                              |

|    | 7.5<br>7.6<br>7.7                      | Trace                                                       | Compiler Overview                                                                                                                                                                                                                                                                                     | . 80                         |

|    |                                        | 7.7.1<br>7.7.2<br>7.7.3<br>7.7.4<br>7.7.5<br>7.7.6<br>7.7.7 | Pass 1 - Create 'Symbol Table'  Pass 2 - Perform local compiler optimizations  Pass 3 - Generate virtual processor emulation code  Pass 4 - Generate register allocation directives  Pass 5 - Memory and Register Assignment  Pass 6 - Peephole Optimization  Pass 7 - Target Machine Code Generation | . 83<br>. 83<br>. 84<br>. 85 |

|    | 7.8                                    | Evalua                                                      | ation of Trace Compilation                                                                                                                                                                                                                                                                            |                              |

|    |                                        | 7.8.1<br>7.8.2                                              | Trace Compilation Performance                                                                                                                                                                                                                                                                         | . 86                         |

|    |                                        |                                                             | 7.8.2.1 Code Generation                                                                                                                                                                                                                                                                               | . 86                         |

|     |                   |                         | 7.8.2.4                                                        | Summ                                    | ary of T                                       | Trace C       | Compil    | lation  | Eva  | luati | on   | • • |     |     | <br>    | <br>88                       |

|-----|-------------------|-------------------------|----------------------------------------------------------------|-----------------------------------------|------------------------------------------------|---------------|-----------|---------|------|-------|------|-----|-----|-----|---------|------------------------------|

|     | 7.9               | Conclu                  | isions abo                                                     | out the                                 | Virtual                                        | Machi         | ne En     | nulatio | on M | [etho | odol | ogy |     |     | <br>• • | <br>89                       |

| IV  | <i>r</i> ]        | Evalu                   | ating                                                          | Mass                                    | ively                                          | Para          | allel     | Arr     | ay   | Co    | mŗ   | or  | en  | ts  |         | 91                           |

| 8.  | DATA              | ратн Е                  | Evaluati                                                       | on                                      |                                                |               | . <b></b> |         |      |       |      |     |     |     | <br>    | <br>. 93                     |

|     | 8.1<br>8.2<br>8.3 | Datapa                  | urrent M<br>ath Evalu<br>arameter                              | ator O                                  | verview                                        |               |           |         |      |       |      |     |     |     | <br>    | <br>95                       |

|     |                   | 8.3.1<br>8.3.2<br>8.3.3 | System :<br>Array M<br>PE Data                                 | Iodel .                                 |                                                |               |           |         |      |       |      |     |     |     | <br>    | <br>97                       |

|     | 8.4               | Datap                   | ath Evalu                                                      | ator De                                 | etails .                                       |               |           |         |      |       |      |     |     |     | <br>    | <br>102                      |

|     |                   | 8.4.1<br>8.4.2<br>8.4.3 | The Inp The Inp Dictions                                       | ut Mod                                  | el                                             |               |           |         |      |       |      |     |     |     | <br>    | <br>103                      |

|     |                   |                         | 8.4.3.1<br>8.4.3.2<br>8.4.3.3<br>8.4.3.4<br>8.4.3.5<br>8.4.3.6 | Left as<br>Bit Op<br>Multip<br>Division | netic, L nd Righ peration plication on ng Poin | t Shift<br>is | • • • •   | • • • • |      |       |      | • • | • • | • • | <br>    | <br>105<br>107<br>107<br>109 |

|     |                   | 8.4.4<br>8.4.5          | Virtual :<br>Translat                                          |                                         |                                                |               |           |         |      |       |      |     |     |     |         |                              |

|     | 8.5<br>8.6<br>8.7 | A Case                  | ating Exis<br>e Study:<br>er Summ                              | sting Ma<br>Varying                     | achines:<br>; ALU \                            | An Ex         | xampl     | e       |      |       |      |     |     |     | <br>    | <br>112<br>114               |

| 9.  | Мем               | ory Ev                  | /ALUATIO                                                       | N                                       |                                                |               |           |         |      |       |      |     |     |     | <br>    | <br>. 117                    |

|     | 9.1<br>9.2        |                         | IPA Mem                                                        |                                         |                                                |               |           |         |      |       |      |     |     |     |         |                              |

|     |                   | 9.2.1<br>9.2.2          | Evaluati<br>Evaluati                                           |                                         |                                                |               |           |         |      |       |      |     |     |     |         |                              |

|     | 9.3               | Chapte                  | er Summ                                                        | ary                                     |                                                |               |           |         |      |       |      |     |     |     | <br>    | <br>127                      |

| 10. | Соми              | MUNICA                  | TION NE                                                        | TWORK                                   | 3                                              |               |           |         |      |       |      |     |     |     | <br>    | <br>. 129                    |

|     | 10.2              | Curren                  | in Comm<br>nt MPA C<br>IPA Com                                 | Commun                                  | nication                                       | Netwo         | rks .     |         |      |       |      |     |     |     | <br>    | <br>131                      |

|     |                   | 10.3.1                  | Mesh an<br>Circuit S                                           | d Broad                                 | icast No                                       | etwork:       | s         |         |      |       |      |     |     |     | <br>    | <br>136                      |

|     |                   |                         | 10.3.2.1<br>10.3.2.2<br>10.3.2.3                               | The C                                   | ircuit-S                                       | witched       | d Netv    | vork S  | Simu | lator |      |     |     |     | <br>    | <br>139                      |

| 10.3.3                     | Packet Switched Networks                       | 141 |

|----------------------------|------------------------------------------------|-----|

|                            | 10.3.3.1 Definitions and Properties            | 142 |

| 10.4 Impler                | mentation and Performance of MVM Communication | 146 |

| 10.4.1                     | Scans                                          | 148 |

|                            | 10.4.1.1 Scan Implementations                  |     |

| 10.4.2                     | Route                                          | 149 |

|                            | 10.4.2.1 Route Implementations                 |     |

| 10.4.3                     | OpRoute: Routing with Combining                | 151 |

|                            | 10.4.3.1 Region OpRoute Implementations        |     |

| 10.4.4                     | Region Broadcast                               | 152 |

|                            | 10.4.4.1 RegionBroadcast Implementations       |     |

| 10.5 Chapt                 | er Summary                                     | 153 |

|                            |                                                |     |

| V Result                   | ts and Future Directions                       | 155 |

| 11. CASE STUDY             | Y IN MPA EVALUATION                            | 157 |

|                            | of MPA Evaluation                              |     |

| 11.2.2                     | The ARPA IU Benchmark II                       | 160 |

| 12. Conclusion             | ٧                                              | 164 |

| 12.2 Contri<br>12.3 Future | ary                                            | 166 |

| Denvisor                   |                                                |     |

# LIST OF TABLES

| <b>Fable</b> | P                                                                                                                                                                                    | age |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1          | Partial list of applications being run by end-users on the Cambridge Systems DAP.                                                                                                    | 40  |

| 4.2          | Partial list of applications that have been developed by third-party vendors to run on the MasPar MP1 and MP2.                                                                       | 41  |

| 4.3          | List of test suite tasks with description and characteristics                                                                                                                        | 54  |

| 6.1          | Plane data types supported by the ICL programming language                                                                                                                           | 68  |

| 6.2          | Operations supported in the augmented ICL programming language. C++ methods are shown in sans serif type face                                                                        | 69  |

| 6.3          | When a network does not support a construct directly, it must be emulated. Those emulations not referenced are straightforward                                                       | 70  |

| 7.1          | Shown is the part of the MPA virtual machine instruction set that corresponds to operations executed internally within PEs                                                           | 75  |

| 7.2          | Shown is the part of the MPA virtual machine instruction set that corresponds to interPE communication and array/controller interaction                                              | 76  |

| 8.1          | The legal ALU instruction templates                                                                                                                                                  | 101 |

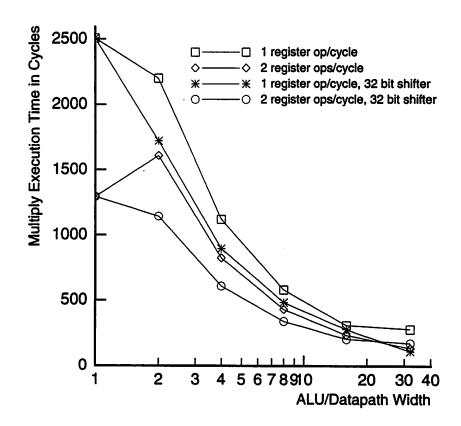

| 8.2          | Execution times of the 32-bit multiply instruction as a function of ALU/datapath width as the number of register operands per cycle is varied and a 32 bit shifter register is added | 108 |

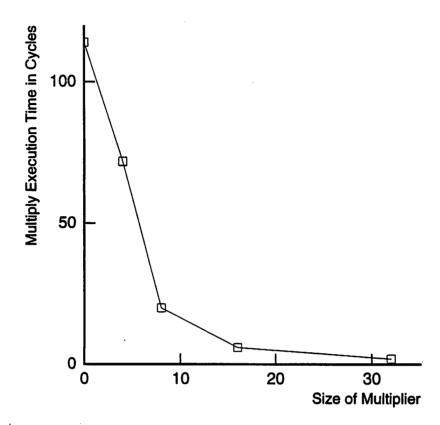

| 8.3          | Execution times of the 32-bit multiply instruction as a function of multiplier size and ALU/datapath width                                                                           | 109 |

| 8.4          | Execution times of the single precision floating point add instruction as a function of ALU/datapath width and various other features                                                | 111 |

| 8.5          | Execution times of the single precision floating point multiply instruction as a function of ALU/datapath width and various other features                                           | 111 |

| 8.6          | Parameters that comprise the CAAPP-like model                                                                                                                                        | 113 |

| 8.7          | Some of the instruction times derived from the CAAPP-like model. For comparison, instruction times for the actual CAAPP are shown                                                    | 114 |

| 10.1         | This table shows which communication instruction/network combinations are supported directly and which require emulation.                                                            | 148 |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

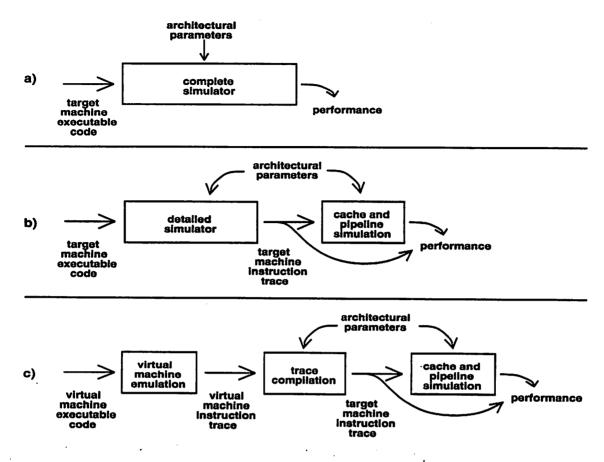

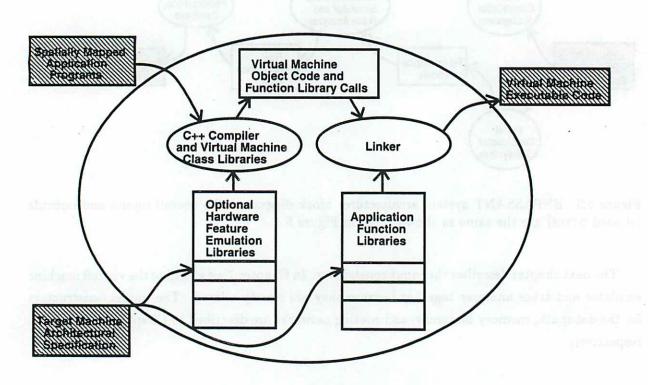

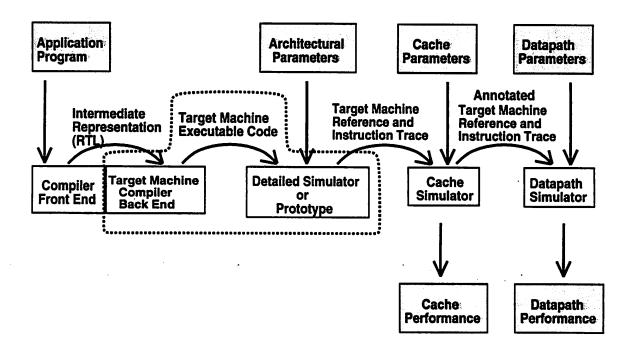

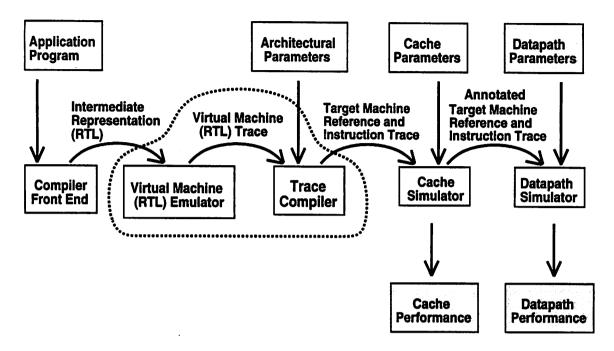

| 1.1    | Block diagrams of three possible methods of evaluating a class of architectures:  a) complete simulation, b) trace-driven simulation, and c) virtual machine emulation and trace compilation                                            | . 6  |

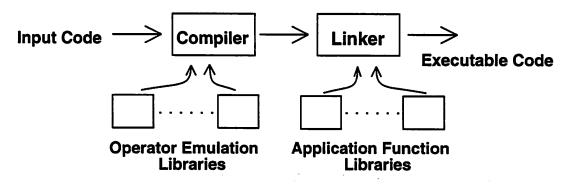

| 1.2    | Portability requires libraries to emulate unavailable hardware and to provide different versions of algorithms as called for by variations in hardware support.                                                                         | . 7  |

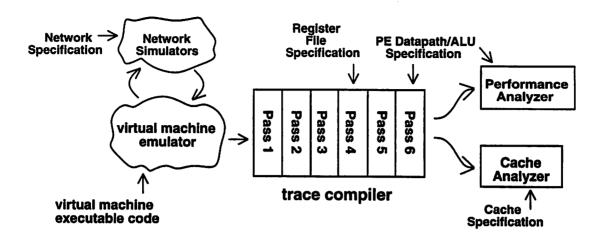

| 1.3    | The different components of the architectural design space are specified and evaluated in various parts of ENPASSANT                                                                                                                    | . 10 |

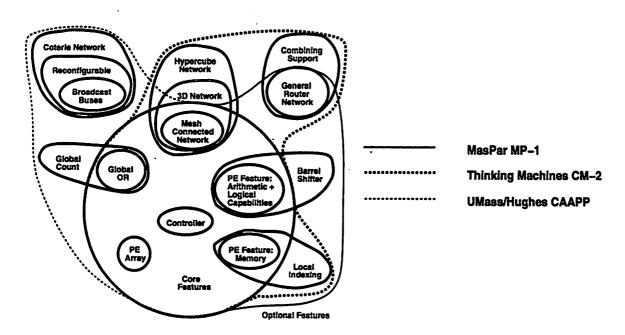

| 3.1    | The MPA architectural design space                                                                                                                                                                                                      | 32   |

| 4.1    | Synthetic 256x256 8 bit gray scale image used as input for the second ARPA IU Benchmark                                                                                                                                                 | . 47 |

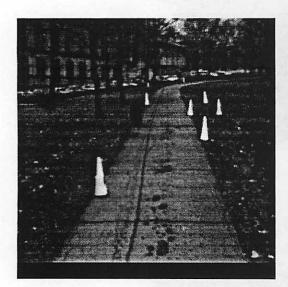

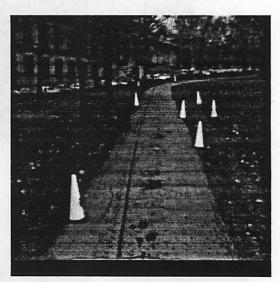

| 4.2    | Two 256x256 8 bit gray scale images used as input for the correspondence matcher                                                                                                                                                        | . 48 |

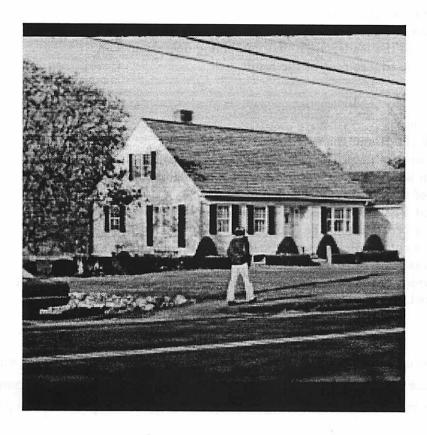

| 4.3    | The 256x256 8 bit gray scale image used as input by the two line finders and the curve-fitting filter                                                                                                                                   | . 49 |

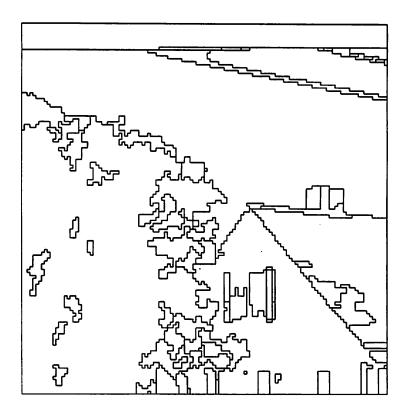

| 4.4    | Edge image corresponding to the 256x256 32 bit region label image of a partial segmentation of the gray scale image shown in Figure 4.3. Used as input for the region merging segmentation procedure                                    | . 51 |

| 4.5    | Two 256x256 floating point displacement images produced as output by the correspondence matcher and used as input for the Dutta depth from motion procedure. The left image is the X displacement and right image is the Y diplacement. | . 53 |

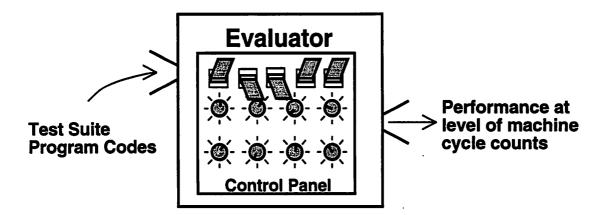

| 5.1    | An ideal evaluation system would resemble a black box with a console and be fast, easy to use, accurate, and flexible.                                                                                                                  | . 58 |

| 5.2    | Shown are representations of three massively parallel arrays (MPAs) as collections of core and optional architectural features                                                                                                          | . 58 |

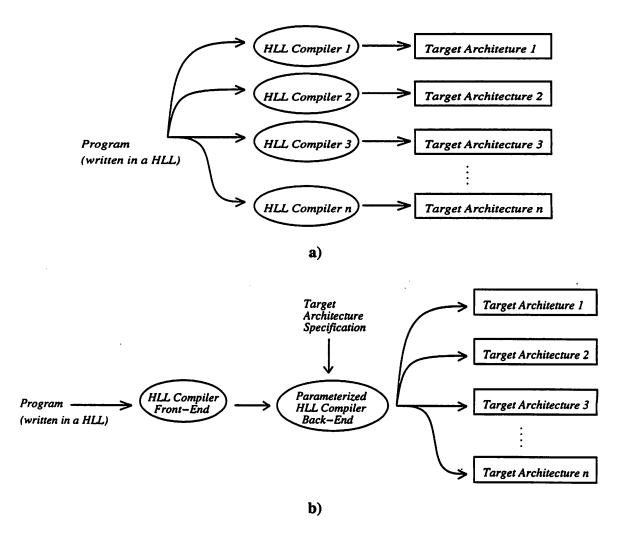

| 5.3    | Shown are two portable High-Level Language schemes: a) A completely separate compiler for each target architecture, b) the compiler front-end is reused                                                                                 | . 60 |

| 5.4    | ENPASSANT system architecture: highest level view                                                                                                                                                                                       | 62   |

| 5.5    | ENPASSANT system architecture: block diagram. The overall inputs and outputs (shaded boxes) are the same as shown those in Figure 5.4                                                                                                   | . 63 |

| 6.1    | Input Constructor Subsystem                                                                                                                                                                                                             | 64   |

| 7.1 | One view of trace-driven simulation                                                                                                                                                                                         |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.2 | How to use the virtual machine methodology and trace compilation to evaluate architectures                                                                                                                                  |

| 7.3 | Macro-instructions are issued by the host to the controller, which generates and issues the micro-instructions instructions actually executed by the PEs 78                                                                 |

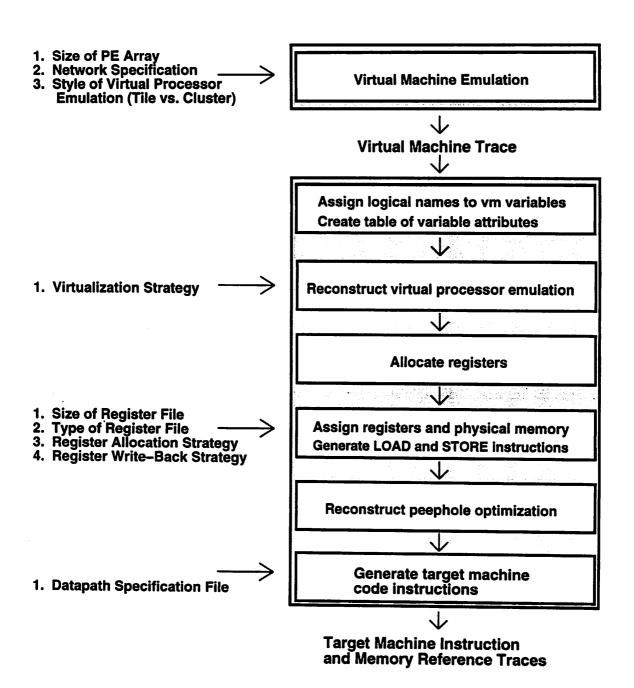

| 7.4 | The virtual machine trace is passed through a series of transformations to reconstruct the target machine instruction and memory reference traces                                                                           |

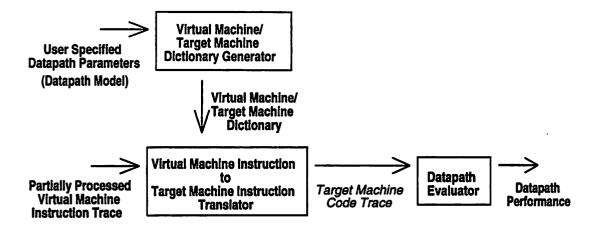

| 8.1 | Datapath Evaluator block diagram. The input trace is the output from Pass 6 of the trace compiler. The target machine code trace is only required for pipelined datapath evaluation                                         |

| 8.2 | The MPA system space                                                                                                                                                                                                        |

| 8.3 | The MPA array space                                                                                                                                                                                                         |

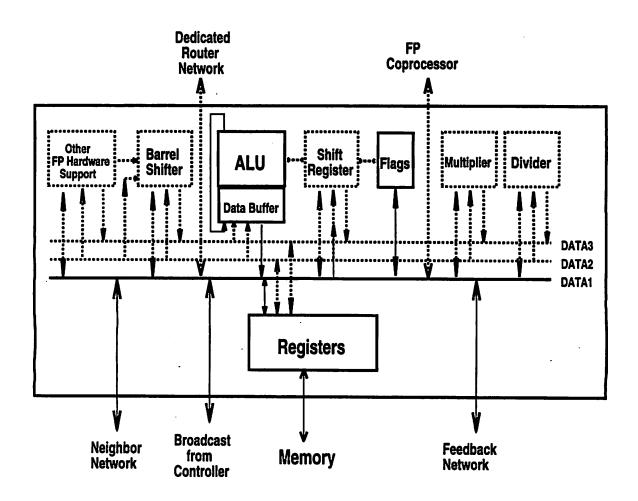

| 8.4 | The generic MPA ALU/datapath model                                                                                                                                                                                          |

| 8.5 | The effect of varying the ALU and internal datapath widths, and presence of a 32-bit shift register on the absolute execution time of the 32-bit integer multiply.108                                                       |

| 8.6 | Effect of adding dedicated multiplier circuit of various sizes on the execution time of the 32-bit integer multiply. Zero on the X-axis indicates no multiplier 110                                                         |

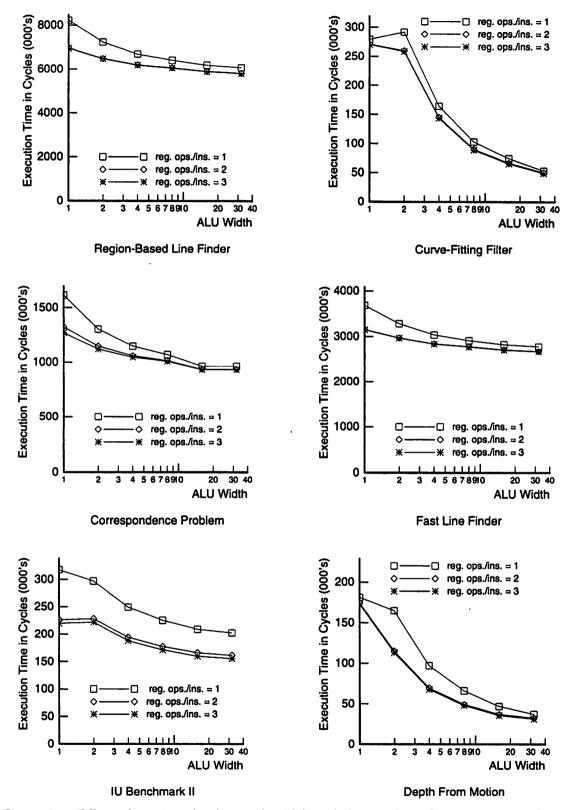

| 8.7 | Effect of varying the datapath width and the number of register operands per target machine instruction. All programs were run on a CAAPP-like model with a register file size of 40 bytes and a virtualization factor of 1 |

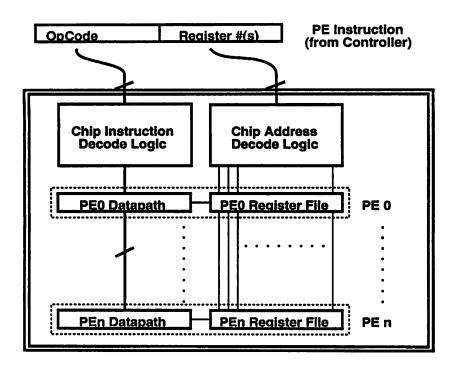

| 9.1 | Shown is a representation of a typical MPA PE chip. Note that there are only single instruction and register address decoders                                                                                               |

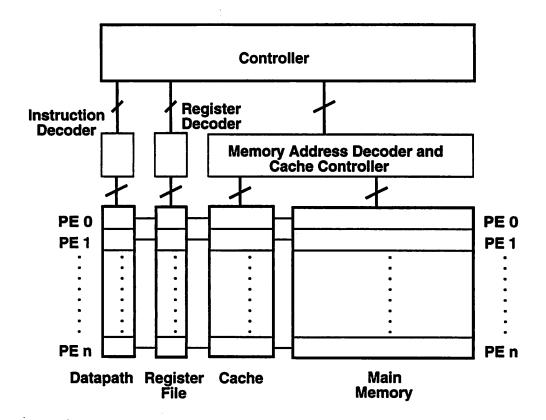

| 9.2 | Shown is the MPA PE memory design space. Note that all PEs share the same controllers                                                                                                                                       |

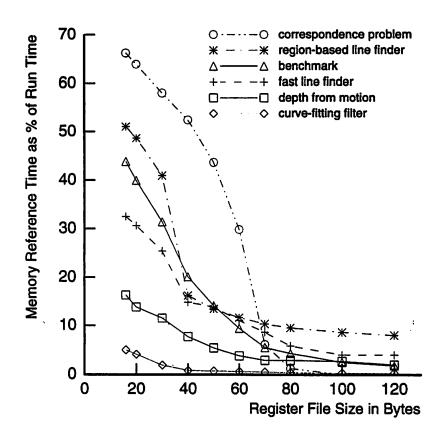

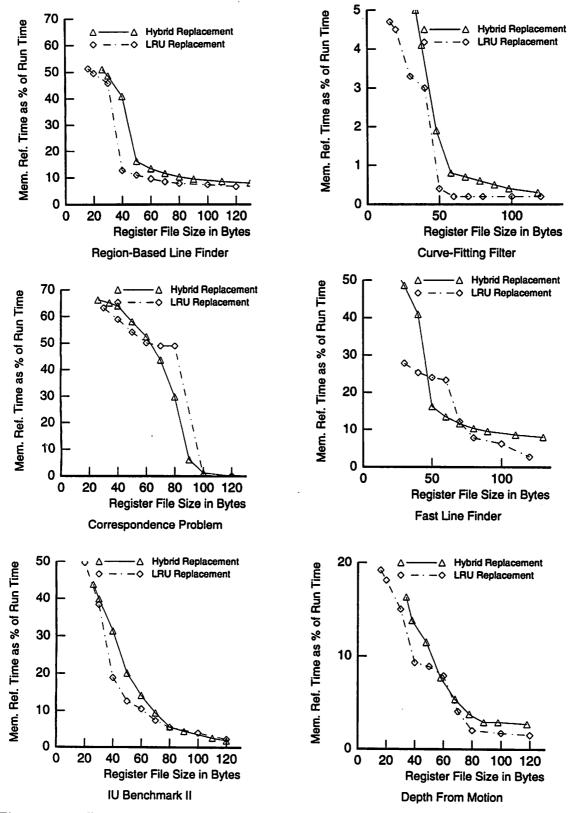

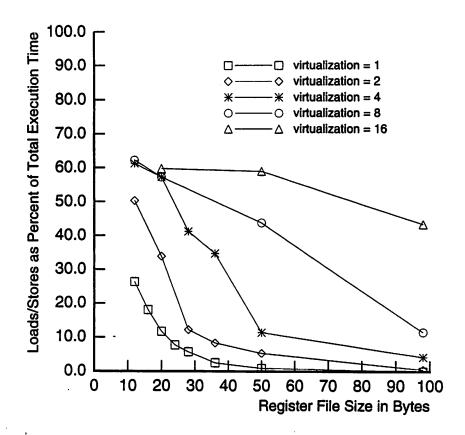

| 9.3 | Effect of the register file size on the fraction of program execution time spent on memory references. A CAAPP-like model is used                                                                                           |

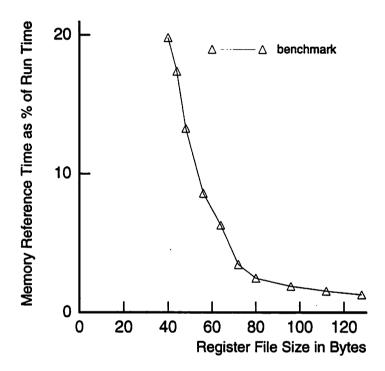

| 9.4 | Detail Figure 9.3. Note that at this resolution the location of the knee can be more tightly bounded                                                                                                                        |

| 9.5 | Effect of dynamic register replacement policy on the total cost of memory references for several test suite programs                                                                                                        |

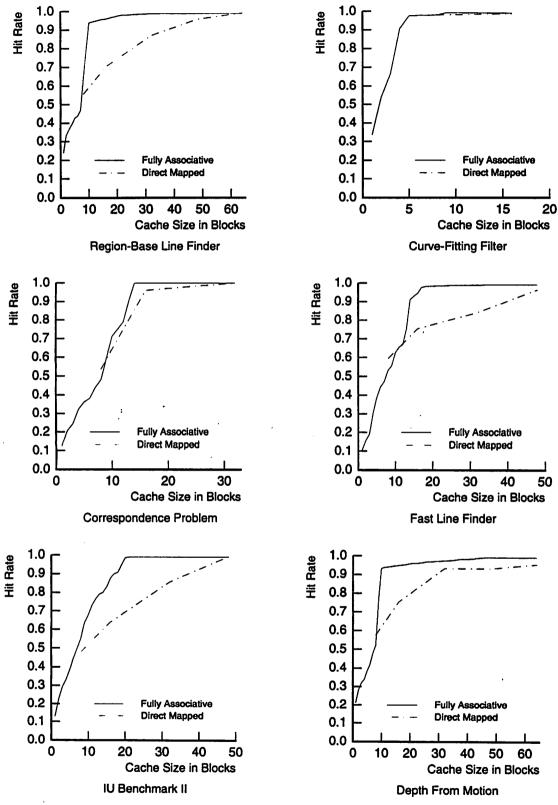

| 9.6 | Comparision of fully associative and direct mapped cache performance 126                                                                                                                                                    |

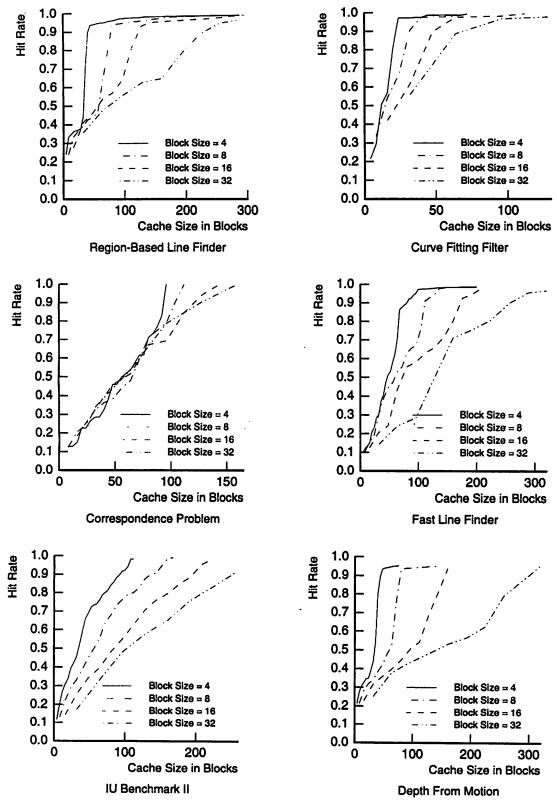

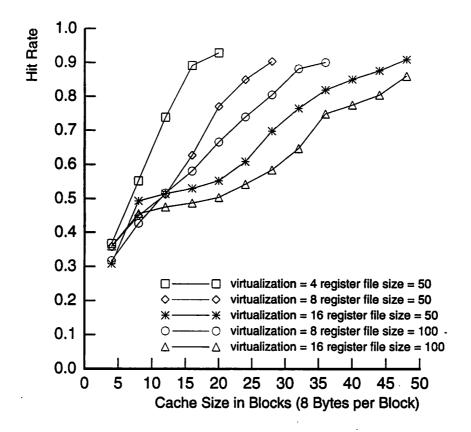

| 9.7 | Effect of varying the cache block size on the relationship between the hit rate and the overall cache size. The cache is fully associative                                                                                  |

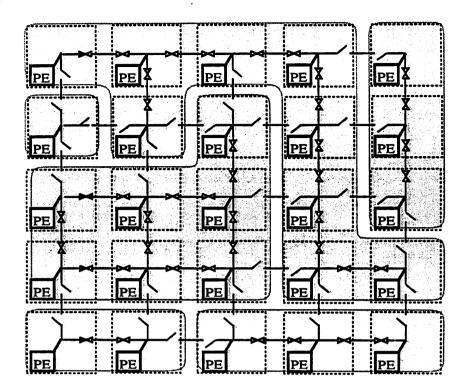

| 10.1  | In a typical MPA communication scheme, each PE has connections to both nearest-neighbors and to a dedicated router network                                                                                        | l <b>32</b> |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

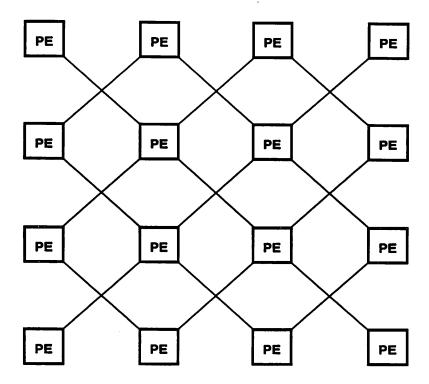

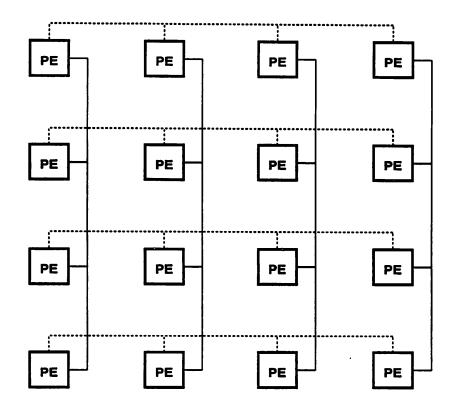

| 10.2  | A 4 × 4 X-grid network                                                                                                                                                                                            | 133         |

| 10.3  | A 5 × 5 coterie network with switches shown in arbitrary settings. Shaded areas denote coteries (the sets of PEs sharing the same circuit). Dashed boxes circumscribe the switches over which each PE has control | 134         |

| 10.4  | A $4 \times 4$ network of horizontal and vertical buses                                                                                                                                                           | L <b>35</b> |

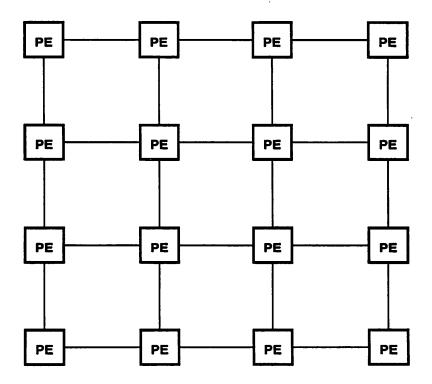

| 10.5  | A 4 × 4 mesh network                                                                                                                                                                                              | .35         |

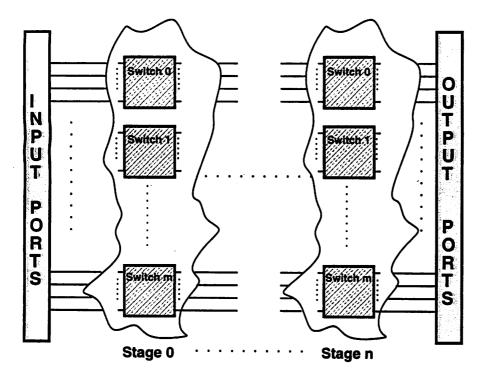

| 10.6  | Shown is a typical multi-stage interconnection network (MIN)                                                                                                                                                      | .38         |

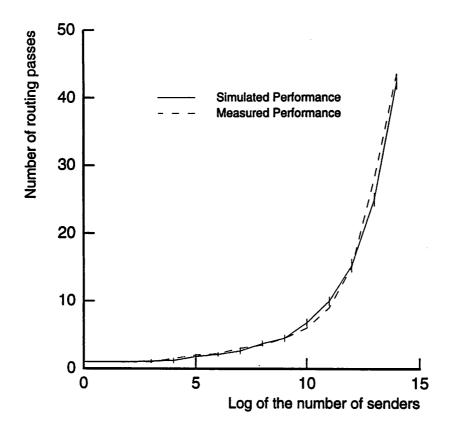

| 10.7  | Number of passes required to route random patterns of various densities on the MP1 router network as obtained by measurement and by simulation using ENPASSANT                                                    | .40         |

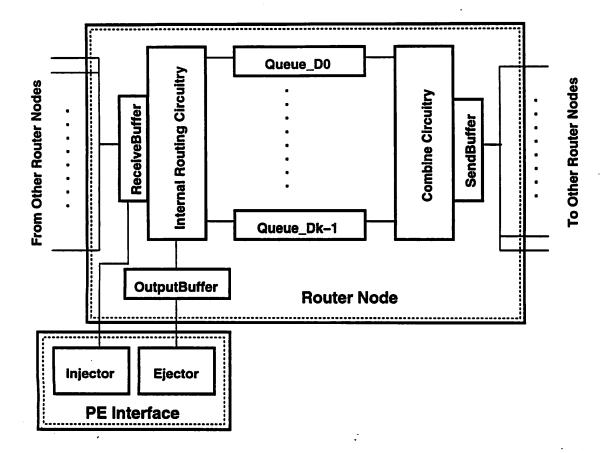

| 10.8  | Shown is the ENPASSANT packet-switched network switch model                                                                                                                                                       | .42         |

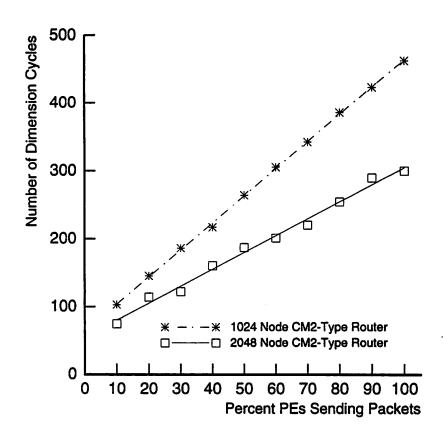

| 10.9  | Number of dimension cycles required to route random patterns of various densities as obtained by simulating CM2-like routing networks. Size of simulated array is 64K PEs                                         | .44         |

| 10.10 | A partially segmented house scene image                                                                                                                                                                           | .45         |

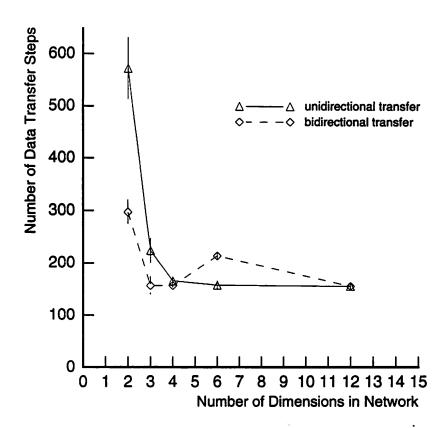

| 10.11 | Effect of varying the number of dimensions on the number of dimension cycles required to reduce the regions shown in images of the type shown in Figure 10.10.1                                                   | .47         |

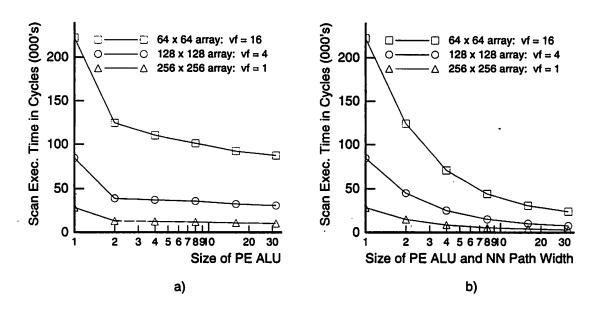

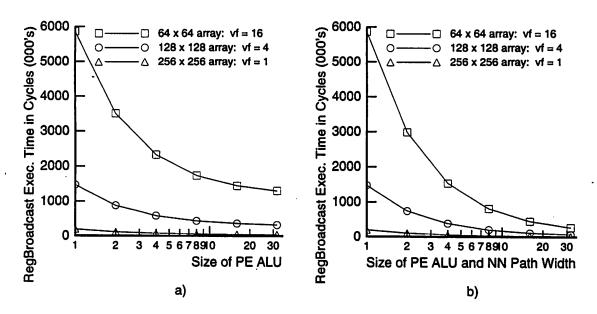

| 10.12 | 2 Effect on +Scan performance on the mesh of varying: a) the ALU datapath width and the number of PEs, and b) also varying the mesh path width                                                                    | .49         |

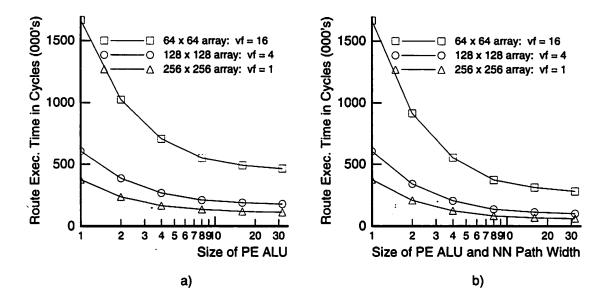

| 10.13 | B Effect on Route performance on the mesh of varying: a) the ALU datapath width and the number of PEs, and b) also varying the mesh path width                                                                    | .51         |

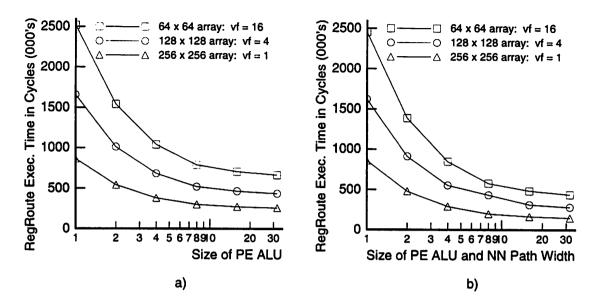

| 10.14 | Effect on +Route performance on the mesh of varying: a) the ALU datapath width and the number of PEs, and b) also varying the mesh path width 1                                                                   | .53         |

| 10.15 | Effect on RegionBroadcast performance on the mesh of varying: a) the ALU datapath width and the number of PEs, and b) also varying the mesh path width                                                            | 54          |

| 11.1  | Effect of array size on the execution time of the IU benchmark                                                                                                                                                    | .59         |

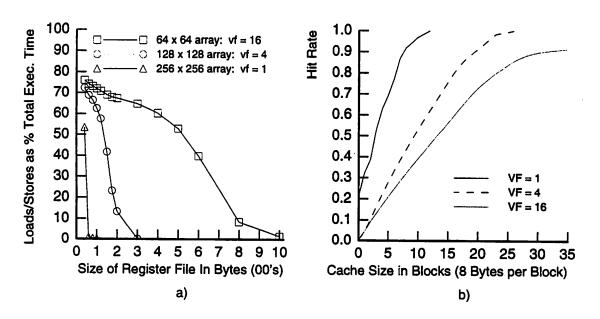

| 11.2  | Effect of the register file size on the percentage of the total execution time spent on memory access for different virtualization factors                                                                        | .60         |

| 11.3  | Plot of the hit rate versus the cache size in 8 byte blocks. The cache is fully associative                                                                                                                       | 61          |

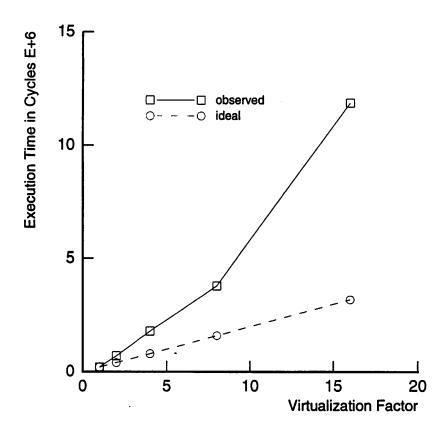

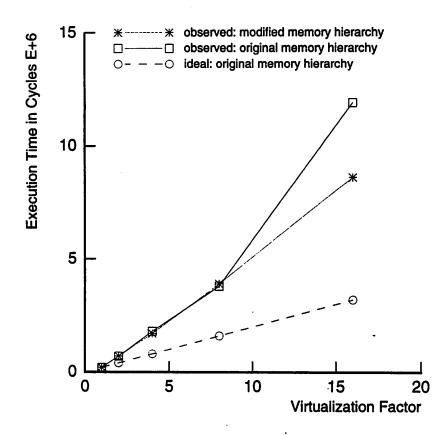

| 11.4 | Effect of PE virtualization factor on the execution time of the IU benchmark as a function. The new memory hierarchy has a cache, but smaller register file size.                                                                                           | 162 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11.5 | For the mesh emulation of the Route instruction: a) effect of the register file size on the fraction of time spent on memory references, and b) effect on the hit rate of the cache size in 8 byte blocks for a fully associative cache and a register file |     |

|      | size of 60 bytes                                                                                                                                                                                                                                            | 162 |

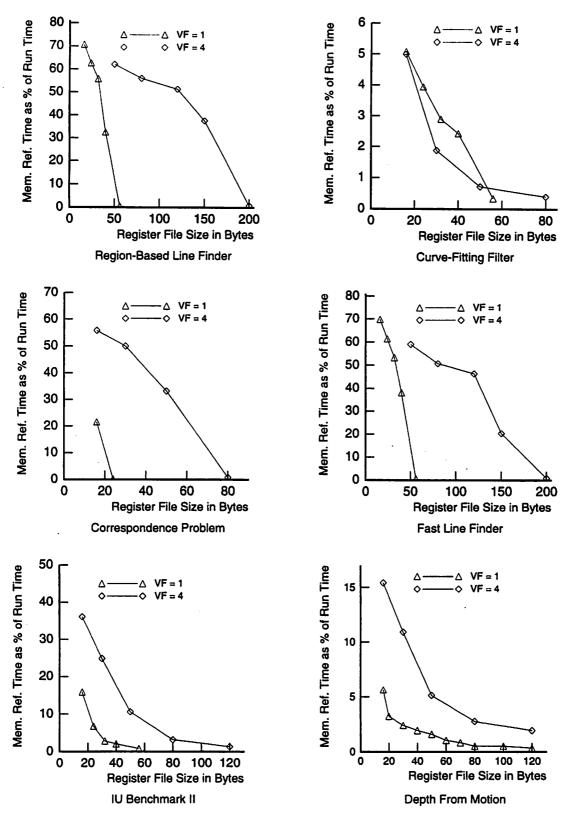

| 11.6 | Shown is the effect of changing the PE virtualization factor from 1 to 4 (reducing the array size by a factor of 4) on the fraction of the execution time spent on                                                                                          |     |

|      | memory references when running several of the test suite programs                                                                                                                                                                                           | 163 |

# PART I INTRODUCTION AND BACKGROUND

#### Introduction

#### 1.1 The Problem

Computer architecture research is being driven from three directions. The first is the need for ever more computing capability: many important applications including modeling, simulation, and intelligent systems (such as those that perform machine vision) require far more processing performance than can be provided by machines existing today or that will be built in the near future. As it has long been realized that we are reaching the limits of the processing capabilities of serial and small-scale parallel designs, it is clear that the only way the desired computation rates are physically possible is through massively parallel processing.

The second direction is that, in the near term, VLSI and packaging technologies continue to improve at phenomenal rates. Feature sizes have been and continue to decrease at roughly a linear rate over time. This has two consequences: switching time—which is roughly proportional to feature size—is also decreasing linearly with time; and more significantly for the purposes of this study, chip device counts are increasing quadratically with time. How best to use these additional devices and how to project their use as more become available are complex but essential issues. See [68] for a review of the effects of changing technology on computer architecture.

The third direction is the realization in the last decade that the approach of increasing any particular aspect of processing capability without thought of how that capability can be applied to a particular application can lead to disappointing results. A new emphasis on empirical methods has been credited with providing the framework within which reduced instruction set computers (RISC) could be developed [46]. These three driving forces together provide the impetus and mechanism for the study of massively parallel processor architecture.

The problem this dissertation addresses is how to make architectural decisions for one class of massively parallel processors—massively parallel array (MPA) computers—with respect to a subset of computationally intensive tasks we call spatially mapped applications. In the class of MPAs we include processor arrays with SIMD control and a number of processing elements (PEs) at least in the thousands. By spatially mapped applications, we mean computations that are derived from real world processes and are characterized by the fact that the spatial relationships inherent in the problem are preserved as the data are mapped to the processor array.

The solution we propose involves—at its highest level—the application of the empirical methods mentioned above. After all, in designing any complex device a systematic approach is desirable: the greater the number and the broader the range of alternatives that are examined closely, the better the chance that a good design will emerge. This is basically what Hennessy and Patterson are saying when they state that the current explosion in microprocessor performance

"... was only possible because a number of important technological advances were brought together with a much better empirical understanding of how computers are used. From this fusion has emerged a style of computer design based on empirical data, experimentation, and simulation [69]."

Our goal in making architectural decisions for MPAs is to build an environment that has the capability of accurately evaluating a large number and broad variety of design alternatives with respect to a realistic workload.

In practice there are trade-offs between the subgoals. In particular, the number of designs that can be examined must be balanced with the accuracy with which they are evaluated. At one extreme, building and testing a prototype examines only one design, although extremely accurately. The alternative to prototyping is simulation: by sacrificing some accuracy, a great deal of flexibility can be gained. Although prototyping and simulation are both essential architectural tools, simulation, because of its flexibility, generally precedes prototyping in the design process. And since relatively little simulation has been done in the domain of MPA architectures, that is the method on which we shall concentrate in this dissertation.

#### 1.2 Issues in MPA Evaluation

The analysis of MPA architectures has not yet employed empirical techniques to examine more than a small part of the design space. Most previous architecture studies in this domain have been based on either mapping sample algorithms to architectures (e.g. [51]), requirements analysis (e.g. [139]), or feedback from benchmarks (e.g. [144]). The first two of these methods have served their purpose in making 'first cuts' at machine architectures, but now these need to be extended to yield more specific and detailed results. The third has yielded detailed results about specific designs, but has not illuminated much of the design space.

The difficulties that have prevented comprehensive studies of the kind we propose—besides the inherent complexity of such a task—are the computational intractability of the simulations and the programmability of the test suite. These are now discussed in turn, together with a preview of their solutions. But first, we define two terms: 1) target machine refers to the machine or design to be simulated, and 2) host machine refers to the machine on which the simulation is being run.

# 1.2.1 Computational Intractability

The simulation of MPAs at the machine instruction level requires orders of magnitude more processing than the simulation of a serial processor. This is because of the large number of processing elements (PEs) that need to be simulated and because of the size and complexity of some MPA interconnection networks. For example, running a modest sized program that takes milliseconds to run on a target machine (the CAAPP [147]) and seconds to run on a SUN SPARC-2 workstation can take hours, or even days, to simulate on that same workstation. Such

long turnaround times make it impossible to examine a large number of design alternatives, even with a substantially faster host machine.

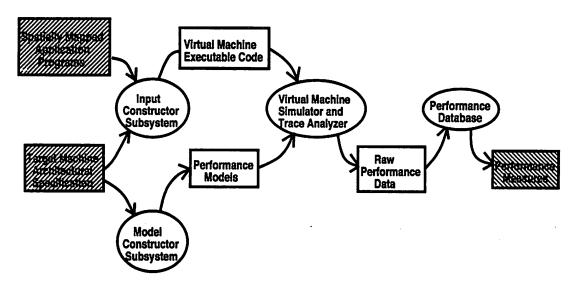

There are two keys to overcoming the computational intractability of the simulations: simulating at higher (less detailed) level, and reusing simulations for multiple designs. Both of these principles are employed in the commonly used method of trace-driven simulation. Trace-driven simulation is a two part process. In the first part, a trace is generated using a slightly less than comprehensive model of the target machine. We call this a detailed simulation, as opposed to a complete simulation where all components would be modeled. For example, though the instruction and register architectures are specified in a detailed simulation, typically the cache and pipeline architecture are not. This brings us to the second part of the process: the trace can now be used any number of times to drive simulators of those components that were not initially modeled. Trace-driven simulation works because the design of the components being modeled does not affect the program execution that drives the generation of the initial trace.

Trace-driven simulation, however, does not help us address the problem of computational intractability (nor of programmability and portability). The initial detailed simulation is still too costly. In fact, for target machines with simple PE ALUs the detailed and the complete simulation are identical. Instead, our approach is to run the initial simulation and trace generation at an even higher level—on what we call the MPA virtual machine. The MPA virtual machine is the minimum configuration necessary to run a program written in a generic MPA language. The trace generated from the virtual machine emulation is then passed through a series of transformations with respect to the parameters and features of the target architecture until a trace emerges that closely resembles the trace that would have been generated by a detailed simulation of that target machine. We call this process of trace reconstruction trace compilation.

Together, virtual machine emulation and trace compilation are typically 30 to 50 times faster than detailed simulation. Also, traces need to be generated far less frequently. See Figure 1.1 for block diagrams of the different methods described in this subsection.

#### 1.2.2 Programmability and Portability

There are two portability problems. The first is that there does not exist a high-level language that is supported for more than a small number of MPAs. The second is that MPAs are such a broad architectural class that porting code among target architectures (or potential designs) sometimes requires that functions be recoded to use different algorithms. We now describe these problems.

1. It is essential that programs written for our simulation system be portable in the sense that they are compilable and executable no matter what target machine we would like to examine. This is where the virtual machine methodology yields another benefit: as long as the input program runs on the virtual machine emulator, the particulars of the target machine are irrelevant.

Figure 1.1. Block diagrams of three possible methods of evaluating a class of architectures: a) complete simulation, b) trace-driven simulation, and c) virtual machine emulation and trace compilation.

There is, however, an important issue that must be addressed before this can happen: certain language constructs that are an essential part of the programmer's model of the MPA virtual machine are not supported directly in hardware by all target machines. In this situation, those language constructs must be emulated using features that *are* available on the target architecture.

2. Porting code among MPA architectures (or potential designs) sometimes requires that functions be recoded to use different algorithms. Otherwise the appropriate features will not be used properly and the results will be skewed.¹ This problem can be viewed as balancing programmability with fairness and accuracy: either the benchmark is task oriented and requires a coding effort for each significantly different platform, or it is source code oriented and maps unevenly to different designs. Vision architecture benchmarks, for example,

<sup>&</sup>lt;sup>1</sup>This version of the portability problem can usually be handled in serial architecture studies by having a high quality compiler available for each target architecture. This is not the case for massively parallel architectures for reasons that will be discussed later.

have leaned towards being task oriented [120, 124, 148] and have therefore depended on independent efforts by each architecture's advocates to code the test suite. This has again limited the performance measurements to a few specific machines.

To maintain fairness while still allowing the search of a significant part of the design space, we use a combination of task oriented test suite specification and architecture dependent object libraries. The basic idea is to provide different versions of particular sub-tasks to those architectures that require them, but to do this only when they are needed.

See Figure 1.2 for block diagrams of how the emulation and task libraries fit in the system.

Figure 1.2. Portability requires libraries to emulate unavailable hardware and to provide different versions of algorithms as called for by variations in hardware support.

#### 1.3 The Approach

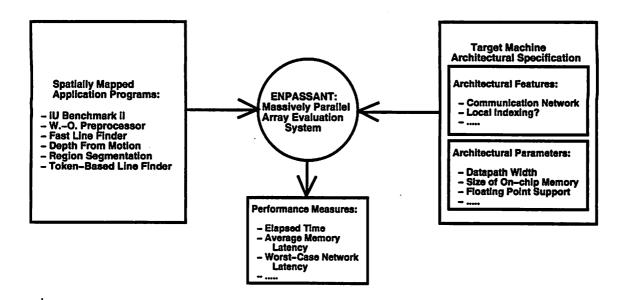

The overall problem addressed in this dissertation is how to create a mechanism with which to investigate MPA architectures by simulating instances of target machines with respect to real program executions. The primary result is an evaluation environment for MPA architectures that is accurate, flexible, efficient, fair, and programmable. We call it ENPASSANT (ENvironment for PArallel System Simulation Analysis Tools).

To get from the overall problem to the primary result involves solving many subproblems besides those mentioned in the previous section. These key issues and our approach in addressing them are briefly discussed in this section.

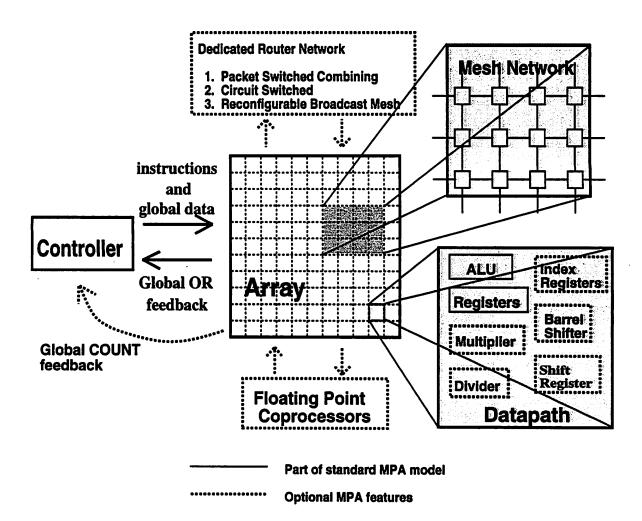

#### 1.3.1 The MPA Architecture Space

The architecture space, or the set of features and parameters that form the domain of MPA architectures can be partitioned into those components which are common to all machines in the class, and those that are optional.

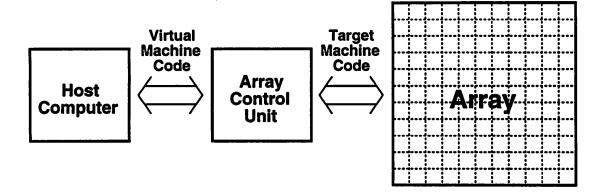

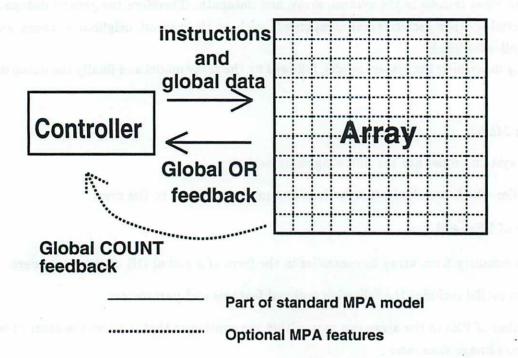

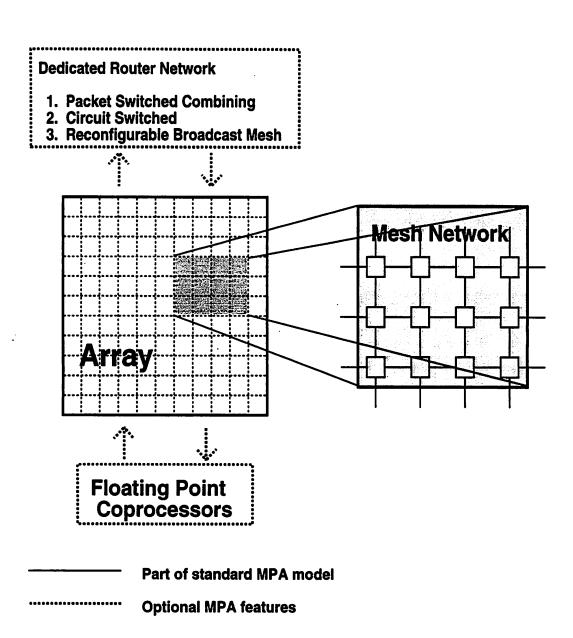

We assume that all target architectures in our study are composed of a controller and an array of PEs running in SIMD mode. The controller broadcasts instructions and global data to the array and has the capability of reading global status in the form of a global OR. The PEs in the array are simple, having no micro-sequencer or instruction autonomy other than the choice of participating or not participating in a particular instruction. The PEs are interconnected via a mesh network, or a network that can efficiently emulate mesh connections.

The optional features include dedicated routing networks that perform broadcast, permutation, scan, and reduction operations; floating point support either in the form of co-processors, or local hardware enhancements such as barrel shifters; other PE features such as multipliers; PE cache memory; and many others. Many features have parameters that can be varied: examples are the number of registers, the ALU width, and the dimensionality of the router network.

#### 1.3.2 Selecting a Test Suite

A problem with current MPA architecture research is that the benchmark test suites may not have accurately reflected the workload of spatially mapped computations. They have often been restricted to relatively small computations and a set of well-known—but not necessarily representative—algorithms. Recent efforts have gone some way in changing this (see e.g. [148]).

We address the problem of proper workload selection by including applications in our test suite that are in current use; that have more than trivial size, ranging from a few hundred to a few thousand lines of code; and that, as much as possible, span the space of the types of computations likely to be encountered in practice.

#### 1.3.3 Creating a Generic MPA Language

As we mentioned above, there does not currently exist a language supported by even a small number of MPA target architectures. A minimum requirement of such a language is that it give the programmer access to the features available on the particular target machine for which the code is intended. Since our MPA language is meant for not just one target architecture, but rather for the entire class, the programmer's model must contain access to the union of the features available on MPAs.

The basis for our 'generic' MPA language is ICL, a parallel class library extension to C++ [39]. First developed for the IUA [147], we have extended it to support the aforementioned union of MPA features. In other words, the ICL programmer's model is a generic MPA; what we have already referred to as the MPA virtual machine model.

#### 1.3.4 Emulating Operators for Optional Features

A programmer will often select a language construct for a particular task on the basis of convenience, rather than on performance. And in any case, once a program has been written in ICL, we want to be able to use it to evaluate any MPA target machine. That means that a

construct C that was included in ICL to give the programmer access to hardware feature F that is available on some, but not all, MPAs, must also be executable on target machines that do not have F. To do this requires that C be emulated with constructs that are available on the target machine. Examples include emulating permutation routing on MPAs with no dedicated router network by using nearest-neighbor connections, and emulating region broadcast on machines with no broadcast network with a network that efficiently executes scan operations.

#### 1.3.5 Application Library Functions

As the previous subsection illustrates, porting a code directly from one processor to another means that available hardware features are sometimes used suboptimally. To prevent this from skewing results, at least in the most serious cases, we have constructed an application function library. Those sub-tasks within the benchmark programs whose choice of algorithm is hardware dependent have separate versions provided. The appropriate version is automatically selected according to the target architecture. Examples of these tasks are labeling connected components and finding convex hulls.

#### 1.3.6 MPA Virtual Machine Emulation and Trace Generation

The method we use to emulate the MPA virtual machine is to compile the ICL test suite program directly onto the host machine and then run it. Directives are embedded in the host machine executable code to generate a trace record for every virtual machine instruction that is emulated.

#### 1.3.7 Trace Compilation

Virtual machine code is in some ways analogous to code generated by the front end (the machine independent part) of a compiler. The trace is necessarily also machine independent. The method we use to generate a target machine instruction trace from the virtual machine trace is analogous to running code in an intermediate representation through the back end (machine dependent part) of that same compiler. The functions performed include register allocation and assignment, target machine instruction generation, and peephole optimization.

#### 1.3.8 Evaluating MPA Components

The purpose of ENPASSANT is to evaluate MPA designs. However, much efficiency can be gained if all design components are not specified or evaluated simultaneously. For convenience, we partition the space of MPA components being evaluated into four distinct sets: the first three are the router networks, the registers, and the cache; the fourth consists of the remaining features including the PE internals. See Figure 1.3 for a block diagram of where the specification and computation occurs for the evaluation of the different components.

We now give some examples.

Figure 1.3. The different components of the architectural design space are specified and evaluated in various parts of ENPASSANT.

- The performances of dedicated router networks are sometimes highly data dependent. They

must therefore be at least partially simulated during virtual machine emulation.

- The register file architecture affects the generation of the memory reference trace which

takes place during pass 4 of the trace compiler. It must therefore be specified at that point.

The effect of the register file specification can be measured further downstream, however.

- The cache, which depends on the virtual memory address trace, can be evaluated independently from the rest of the architecture. This situation is identical to that in trace-driven simulation.

- All other architectural components, including the PE datapath and ALU, the array to

controller feedback, and the nearest-neighbor and broadcast communication are specified

during the last phase of trace compilation. This is where virtual machine instructions are

expanded into target machine instructions. The performance analyzer uses the resulting

target machine instruction trace to obtain the performance.

## 1.3.9 Virtual Processor Support

A general rule in running codes on MPAs is that the number of data elements greatly exceeds the number of PEs. The way this situation is usually handled is to map the data for one element to each *virtual* PE, and then have the physical PEs emulate as many virtual PEs as necessary. ENPASSANT supports two types of PE to virtual PE mapping: block and cyclic.

Since some of the communication instruction emulations depend on the ratio of virtual to physical PEs (the *virtualization factor*), the processor array size (number of physical PEs) and the mapping style must be specified at run time. The rest of the virtual PE emulation code is generated during trace compilation.

## 1.3.10 Traversing the Evaluation Space

There are at least two uses for ENPASSANT

- 1. to be a tool in examining the basic issues in MPA design, such as processor granularity and the complexity of the inter-PE communication network, and

- 2. to study existing designs, that is, benchmarking and examining the effects of future parameter and feature changes.

These two uses obviously overlap: for example, existing designs are naturally good starting points for searching the MPA architecture space.

Three components of the MPA design space are largely independent from one another. These are the memory hierarchy; the dedicated communication network, if there is one; and the rest of the array, consisting primarily of the PE ALU and datapath, the array to controller feedback, and the nearest neighbor connections. As in all system design, all else being equal, we seek to remove bottlenecks; or conversely, to achieve system balance.

## 1.4 Outline of Results Achieved, Contributions

We now describe the contributions of this work and their significance. We begin with contributions that arise from building the evaluation system.

- ENPASSANT: an evaluation environment for simulating MPA architectures with respect to

real program executions. Especially noteworthy is that the environment is flexible, efficient,

fair, and accurate. The significance is that ENPASSANT will enable architects to explore

the MPA design space in much more detail than was previously possible. No current system

has the flexibility and efficiency necessary to provide this function.

- The virtual machine and trace compilation methodology. Although other evaluation methods improve performance by omitting detail and reusing computation, the idea of a trace compiler that reconstructs virtual PE emulation, register allocation, optimization, and target machine code generation is completely original. The trace compiler has two performance benefits. The first is that it allows us to simulate MPAs at a high level (virtual machine emulation); this gives us more than an order of magnitude speed-up in evaluation time over detailed simulation. The other benefit is that traces need to be generated far less frequently; only when there are changes in the number PEs and the type of communication network. This is in contrast to other methods where the trace would also need to be regenerated for changes in register file size and target machine instruction set. The significance is that our method gives us the efficiency required to systematically explore the MPA design space that is not offered with other methods. Also, the trace compilation method may be useful in some domains where trace-driven simulation is now used because of the reduction in the frequency with which traces need to be generated.

- Selective recoding. By using application function libraries we recode those and only those parts of the applications that require it. A modest programming effort was found to be adequate to enable fair comparisons for the architecture and application domains in this study. The significance is that it seems likely that this result will extend to other application areas and possibly to other architecture domains. Although function libraries (graphics, numerical methods) are ubiquitous, libraries that contain a number of functions—each of which is implemented with multiple algorithms whose choice depends on the architecture—are uncommon. However, work has been done elsewhere in the development of programming methods that allow code to be ported with minimal recoding and little loss in performance [8].

- Portable language. By adding a number of constructs and an emulation library to ICL, we have created a language that allows us to use the same program during the evaluation any MPA target architecture without recoding.<sup>2</sup> Although the idea of emulating optional hardware is an old one (e.g. floating point emulation versus floating point coprocessor), it has not been applied to the emulation of interPE communication instructions on MPAs. In fact, earlier implementation of the emulations would have been difficult as sufficiently efficient algorithms for several of them were only recently developed [70]. The significance is that ICL now has a greater potential to form the basis for a portable language among machines in the MPA class for the class of spatially mapped applications.

- The benchmark test suite. We have assembled a suite of non-trivial programs having diverse arithmetic, communication, and memory requirements. The significance is that together they provides a more complete test bed than was previously available, say, by using the DARPA IU benchmark (see [148]) alone.

The other major contributions of this work are the results that have been derived so far using ENPASSANT. Their significance is that they provide recommendations for the next generation MPA processors. Selected results are as follows.

- Datapath. When the performance of the test suite programs is measured as a function of ALU width, most of the gain occurs when the ALU width is increased from 1 to 8, and especially, very little performance is gained when the ALU is increased from 16 to 32.

- Register file. When the cost of memory references is measured as a function of the number of registers, distinct working sets were found for all programs. This indicates a recommended register set size for future MPAs.

- PE Cache. Associativity has a major effect on PE cache performance: direct mapped cache

must often be 2 to 4 times larger than fully associative to achieve the same performance.

<sup>&</sup>lt;sup>2</sup>Though not necessarily fairly. See previous point.

Also, PE memory references do not have much locality: thus very small block sizes are preferred.

• Packet switched (k-ary n-cube) networks. In an essential application, performance improved little when the dimensionality was increased beyond three (and the bandwidth held constant). Also, bidirectional links provide a large advantage when n=2.

# 1.5 Organization of the Disseration

The rest of the dissertation is organized as follows.

- In Chapter 2 we review the common techniques used in architectural research and especially in architectural evaluation. We find that none of the existing methods meet our requirements.

- In Chapter 3 we describe in detail the MPA design space and the components that will be examined and evaluated.

- In Chapter 4 we review the application space—the types of programs that are typically run on MPAs by end users. From these programs we derive a set of common features. We then present a test suite that spans this feature space.

- In Chapter 5 we give a high-level overview of ENPASSANT.

- In Chapter 6 we describe how ENPASSANT deals with the programmability and portability issues. We discuss the selection of the MPA virtual machine programmer's model and the contents of the application function and operator emulation libraries.

- In Chapter 7 we give the details of the virtual machine and trace compilation methodology. Included are discussions of the issues involved, especially validation and performance.

- In Chapter 8 we begin the descriptions of how we evaluate the components of the MPA

design space with a discussion of the datapath. Also presented are an overview of the

datapaths and ALUs currently in use, the parameterized datapath model we use to abstract

that space, and some case studies of the effects of varying parameters on instruction and

program execution times.

- In Chapter 9 we continue describing component evaluation with register file and cache design. The organization is similar to that in chapter 8.

- In Chapter 10 we examine communication networks. Again, the current design space is presented together with the models we use to abstract those spaces and followed by the case studies.

- In Chapter 11 we present some more sample results that have been obtained using ENPAS-SANT.

- In Chapter 12 we present our conclusions and describe areas of future research.

### CHAPTER 2

# MASSIVELY PARALLEL ARRAY EVALUATION: ISSUES AND REVIEW

Computer architecture research can be viewed in some respects as a search problem. As with most search problems, there are two aspects: creating the search space and traversing it. In this view, creating the architectural search space can be seen as taxonomizing existing designs and incorporating new design alternatives, while traversing the space can be seen as evaluating them.

There are two primary, often inter-related, sources for new architectural alternatives: the application of new technologies to machine design (e.g. integrated circuits), and the invention of new components (e.g. various routing networks). Although there is much active research in these areas, this dissertation will concentrate on the second part of the architecture research problem: how to traverse the space defined by architectural design alternatives.