## SOFTWARE TECHNIQUES TO REDUCE THE ENERGY CONSUMPTION OF LOW-POWER DEVICES AT THE LIMITS OF DIGITAL ABSTRACTIONS

A Dissertation Presented

by

MASTOOREH (NEGIN) SALAJEGHEH

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

September 2012

Department of Computer Science

© Copyright by Mastooreh (Negin) Salajegheh 2012 All Rights Reserved

# SOFTWARE TECHNIQUES TO REDUCE THE ENERGY CONSUMPTION OF LOW-POWER DEVICES AT THE LIMITS OF DIGITAL ABSTRACTIONS

### A Dissertation Presented

by

#### MASTOOREH (NEGIN) SALAJEGHEH

| Approved as to style and content by: |  |   |             |    |

|--------------------------------------|--|---|-------------|----|

|                                      |  |   |             |    |

| Kevin Fu, Chair                      |  | _ |             |    |

|                                      |  | _ |             |    |

| Wayne Burleson, Member               |  |   |             |    |

|                                      |  | _ |             |    |

| Deepak Ganesan, Member               |  |   |             |    |

| Erik Learned-Miller, Member          |  | _ |             |    |

| ,                                    |  |   |             |    |

|                                      |  |   | tment Chair | ce |

This page is intentionally left blank.

#### ACKNOWLEDGMENTS

I would like to express my deepest gratitude to my advisor, Dr. Kevin Fu, for inspiring me and encouraging me for the past five years. I thank him for teaching me how to think, write, and present and I still have a lot to learn from him. I thank him for making me aim high and work hard.

I thank members of my committee, Dr. Wayne Burleson, Dr. Erik Learned-Miller, and Dr. Deepak Ganesan whose advice, feedback, and encouragement have been invaluable.

This thesis would not have been possible without the collaborative work, time, advice, and support of my colleagues in the SPQR lab: Ben Ransford, Shane Clark, Andres Molina, Hong Zhang, Amir Rahmati, Shane Guineau, and Benessa Defend as well as my fantastic collaborators outside of SPQR Lab: Jacob Sorber and Dan Holcomb. I also thank all the students in "Lab" lab for making my life more fun in the lab.

I thank Wendy Cooper for making Halloween scary for me for the first time by setting Halloween the deadline for my dissertation proposal. I also thank her for all of her support and encouragement.

I would like to thank Quinn Stewart for her tremendous help on editing my writings including this thesis.

I would like to acknowledge NSF and UMass CVIP group for funding my graduate studies—of course through my advisor's efforts.

During the past five years in Amherst, I have found many friends who made my life fun and exciting. I thank them all for letting me feel part of a large family.

I greatly thank my parents and my sister who sent me their support and love through phone calls, emails, and Skype screens for the past five years.

Most of all, I would like to thank my husband, Hamed Soroush, who has been my classmate, co-author, and colleague for the past 10 years. Without his non-stop support and encouragement, I would not have been here. He had more confidence in me than I did in myself.

#### ABSTRACT

### SOFTWARE TECHNIQUES TO REDUCE THE ENERGY CONSUMPTION OF LOW-POWER DEVICES AT THE LIMITS OF DIGITAL ABSTRACTIONS

#### SEPTEMBER 2012

MASTOOREH (NEGIN) SALAJEGHEH

B.Sc., SHARIF UNIVERSITY OF TECHNOLOGY

M.Sc., CARNEGIE MELLON UNIVERSITY, INI

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Kevin Fu

My thesis explores the effectiveness of software techniques that bend digital abstractions in order to allow embedded systems to do more with less energy. Recent years have witnessed a proliferation of low-power embedded devices with power ranges of few milliwatts to microwatts. The capabilities and size of the embedded systems continue to improve dramatically; however, improvements in battery density and energy harvesting have failed to mimic a Moore's law. Thus, energy remains a formidable bottleneck for low-power embedded systems.

Instead of trying to create hardware with ideal energy proportionality, my dissertation evaluates how to use unconventional and probabilistic computing that bends traditional abstractions and interfaces in order to reduce energy consumption while protecting program semantics. My thesis considers four methods that unleash energy

vii

otherwise squandered on communication, storage, time keeping, or sensing: 1) CCCP, which provides an energy-efficient storage alternative to local non-volatile storage by relying on cryptographic backscatter radio communication, 2) Half-Wits, which reduces energy consumption by 30% by allowing operation of embedded systems at below-spec supply voltages and implementing NOR flash memory error recovery in firmware rather than strictly in hardware, 3) TARDIS, which exploits the decay properties of SRAM to estimate the duration of a power failure ranging from seconds to several hours depending on hardware parameters, and 4) Nonsensors, which allow operation of analog to digital converters at low voltages without any hardware modifications to the existing circuitry.

#### TABLE OF CONTENTS

|              |                                               | Pag                                                                                                                                                                                                                                                     | ge                              |

|--------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| A            | CKN                                           | OWLEDGMENTS                                                                                                                                                                                                                                             | $\mathbf{v}$                    |

| $\mathbf{A}$ | BST                                           | RACT v                                                                                                                                                                                                                                                  | ⁄ii                             |

| LI           | ST (                                          | OF TABLESx                                                                                                                                                                                                                                              | iii                             |

| LI           | ST (                                          | OF FIGURES                                                                                                                                                                                                                                              | ۲V                              |

| Cl           | НАР                                           | TER                                                                                                                                                                                                                                                     |                                 |

| 1.           | INT                                           | TRODUCTION                                                                                                                                                                                                                                              | 1                               |

|              | 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7 | A Vision for a Cleaner World Thesis Overview CCCP, Secure Remote Storage for RFID Tags Half-Wits, Non-Volatile Storage at Low Voltage TARDIS, Secure Notion of Time for Batteryless Devices Nonsensors, Sensing at Low Voltage Summary of Contributions | . 2<br>. 3<br>. 4<br>. 5<br>. 6 |

| 2.           | LO                                            | W-POWER EMBEDDED SYSTEMS                                                                                                                                                                                                                                | 9                               |

|              | 2.1<br>2.2                                    | Battery-powered Embedded Systems                                                                                                                                                                                                                        |                                 |

|              |                                               | 2.2.1 Computational RFID Tags                                                                                                                                                                                                                           |                                 |

| 3.           |                                               | CP: SECURE REMOTE STORAGE FOR COMPUTATIONAL RFID TAGS                                                                                                                                                                                                   | 13                              |

|              | 3.1                                           | Frequent Power Loss on Tags, but Plentiful External Resources                                                                                                                                                                                           | 14                              |

|              |                                               | 3.1.1 Challenges Due to Energy Scarcity                                                                                                                                                                                                                 | 16                              |

|    | 3.2        | Design                           | n of CCCP                                                                                                                         |

|----|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|    |            | 3.2.1<br>3.2.2<br>3.2.3<br>3.2.4 | Design Goal: Computational Progress on CRFIDs19Checkpointing Strategies: Local vs. Remote20Threat Model21Secure Storage in CCCP22 |

|    |            |                                  | 3.2.4.1 Keystream Precomputation                                                                                                  |

|    |            |                                  | Integrity                                                                                                                         |

|    |            |                                  | 3.2.4.3 Stream Cipher for Confidentiality                                                                                         |

|    |            |                                  | 3.2.4.4 Hole Punching for Counters Stored in Flash                                                                                |

|    |            |                                  | 3.2.4.5 Extension for Long-Term Storage                                                                                           |

|    |            | 3.2.5                            | Power Seasons                                                                                                                     |

|    | 3.3        | Impler                           | mentation                                                                                                                         |

|    |            | 3.3.1                            | Communication Protocol                                                                                                            |

|    | 3.4        | Systen                           | n Evaluation                                                                                                                      |

|    |            | 3.4.1                            | Security Semantics                                                                                                                |

|    |            | 3.4.2                            | Experimental Setup & Methods                                                                                                      |

|    |            | 3.4.3                            | Performance                                                                                                                       |

|    |            |                                  | 3.4.3.1 System Overhead                                                                                                           |

|    | 3.5        |                                  | eations                                                                                                                           |

|    | 3.6        | Summ                             | ary40                                                                                                                             |

| 4. | Ī          | NON-V                            | TS: SOFTWARE TECHNIQUES FOR VOLATILE EMBEDDED STORAGE AT LOW AGES                                                                 |

|    | 4.1<br>4.2 | _                                | ge on Low-Power Devices: Limitations and Challenges                                                                               |

|    |            | 4.2.1<br>4.2.2<br>4.2.3          | Experimental Methodology                                                                                                          |

|    | 4.3        | 4.2.4<br>Design                  | Accumulative Memory Behavior                                                                                                      |

|    | 1.0        |                                  |                                                                                                                                   |

|    |            | 4.3.1                            | Modeling Low-Voltage Flash Memory                                                                                                 |

|    |            | 4.3.2                            | Design Goals                                                                                                                      |

|    |            | 4.3.3                                     | Proposed Methods                                                                                          | 58             |

|----|------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|

|    |            |                                           | 4.3.3.1 In-Place Writes                                                                                   | 58             |

|    |            |                                           | 4.5.5.5 R5-Derger Codes                                                                                   | 00             |

|    | 4.4        | Evalua                                    | ation                                                                                                     | 63             |

|    |            | 4.4.1<br>4.4.2<br>4.4.3                   | Comparison of the Proposed Storage Methods                                                                | 67             |

|    | 4.5        | Applie                                    | cations                                                                                                   | 71             |

|    |            | 4.5.1<br>4.5.2                            | Battery-Powered Electronic Products                                                                       |                |

|    | 4.6        | Impro                                     | vements and Alternatives                                                                                  | 72             |

|    |            | 4.6.1<br>4.6.2<br>4.6.3<br>4.6.4<br>4.6.5 | Slow Writes Hardware Sign Bits and Storing Complements Memory Mapping Table An Ideal, Unrealizable Scheme | 74<br>75<br>76 |

|    | 4.7        | Summ                                      | nary and Future Work                                                                                      | 76             |

| 5. |            |                                           | SRAM-BASED TIME KEEPING FOR EMBEDDED CES WITHOUT CLOCKS                                                   | . 79           |

|    | 5.1        | Time                                      | Keeping in Intermittently-Powered Devices                                                                 | 80             |

|    |            | 5.1.1                                     | Security Threats Due to Absence of a Trustworthy Sense of                                                 | 01             |

|    |            | 5.1.2                                     | Time                                                                                                      |                |

|    | 5.2        | The T                                     | CARDIS Algorithms                                                                                         | 82             |

|    |            | 5.2.1                                     | TARDIS Performance                                                                                        | 84             |

|    | 5.3        | Securi                                    | ing Protocols with the TARDIS                                                                             | 86             |

|    |            | 5.3.1                                     | Implementation and Evaluation                                                                             | 90             |

|    | 5.4<br>5.5 |                                           | rs Affecting SRAM Decay                                                                                   | 93             |

|    |                   | 5.5.1<br>5.5.2 | Memory Decay Mechanisms  Choosing a State to Write |     |

|----|-------------------|----------------|----------------------------------------------------|-----|

|    | 5.6<br>5.7        |                | ative Approachesary                                |     |

| 6. | FU'               | ГURE           | DIRECTIONS: SENSING AT LOW VOLTAGE                 | 109 |

|    | 6.1<br>6.2<br>6.3 | Logger         | g to Digital Converter (ADC)                       | 110 |

|    |                   | 6.3.1<br>6.3.2 | Voltage Sensor                                     |     |

|    | 6.4<br>6.5<br>6.6 | Future         | eations and coordination with Half-Wits            | 116 |

| 7. | RE                | LATEI          | O WORK                                             | 119 |

|    | 7.1<br>7.2<br>7.3 | Non-V          | e Storage for Computational RFID Tags              | 122 |

| 8. | CO                | NCLU           | SION                                               | 127 |

| Al | PPE:              | NDICI          | $\mathbf{E}\mathbf{S}$                             |     |

|    |                   |                | OF DECAY PROBABILITIESPHY                          |     |

| DI | ътт               | OCD A          | DUV                                                | 199 |

#### LIST OF TABLES

| Table | Page                                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1   | My thesis uses unconventional and probabilistic computing that bends traditional abstractions and interfaces in order to reduce energy consumption while protecting program semantics                                              |

| 1.2   | The ADC restricts choices for the CPU voltage supply on microcontrollers because the CPU shares the same power rail as the on-chip ADC                                                                                             |

| 2.1   | Terminology                                                                                                                                                                                                                        |

| 3.1   | CCCP's design goals and techniques for accomplishing each of them                                                                                                                                                                  |

| 3.2   | Variables CCCP stores in nonvolatile memory                                                                                                                                                                                        |

| 3.3   | Comparison of energy required for flash operations on an MSP430F2274. Hole punching often allows CCCP to use a single-word write (2 bytes on the MSP430) instead of a segment erase when incrementing a complemented unary counter |

| 4.1   | Flash memory restricts choices for the CPU voltage supply on microcontrollers because the CPU shares the same power rail as the on-chip flash memory                                                                               |

| 4.2   | Erroneous flash writes at low voltage. Insufficient electrical charge may result in some bits failing to transition from 1 (the initial state) to 0                                                                                |

| 4.3   | Performance comparison of the proposed methods at 1.8 V and 1.9 V.  Error Correction Rate (ECR) shows the effectiveness of the methods                                                                                             |

| 4.4   | Energy consumption and execution time for the accelerometer sensor application. At voltages below the recommended (1.8 V and 1.9 V), in-place writes method with a threshold of two is used 69                                     |

| 5.1 | Practical attacks on intermittently powered devices. These attacks require repeated interactions between the reader and the device.  Throttling the reader's attempts to query the device could mitigate the attacks                                                                                                     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 | Overhead of TARDIS INIT and DECAY procedures measured for TARDIS size of 256 bytes                                                                                                                                                                                                                                       |

| 5.3 | Definition of the terms used to explain the behavior of SRAM decay and the theory behind it                                                                                                                                                                                                                              |

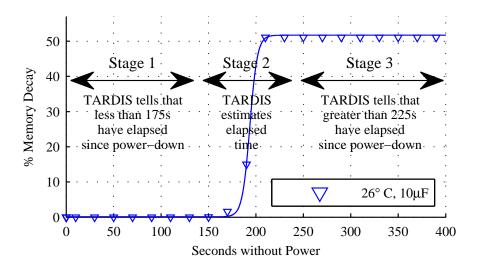

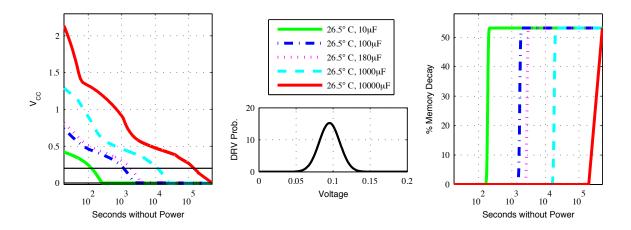

| 5.4 | Estimated time in Stage 1 and Stage 2 of the TARDIS increases as capacitor size increases. The experiments are done on a MSP430F2131 microcontroller at $26.5^{\circ}C$ and an SRAM size of 256 B. Stage 1 is the time after the power failure but before the SRAM decay. Stage 2 represents the duration of SRAM decay. |

| 6.1 | Sensors usually are required to operate at a high supply voltage 117                                                                                                                                                                                                                                                     |

#### LIST OF FIGURES

| Figure | Page                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

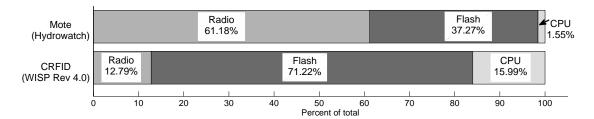

| 1.1    | Per-component maximum power consumption of two embedded devices. Radio communication on the WISP requires less power than writes to flash memory. The relative magnitudes of the power requirements means that a sensor mote favors shifting storage workloads to local flash memory instead of remote storage via radio, while a Computational RFID (CRFID) favors radio over flash                                                        |

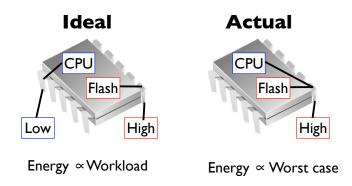

| 1.2    | On a chip, different components have different minimum voltage requirements. Ideally, each component would have separate voltage sources and therefore the energy consumption of the device will be proportional to the workload. In practice, however, a chip has a single power source due to cost constraints. As a result, the energy consumption will be proportional to the worst case voltage requirement regardless of the workload |

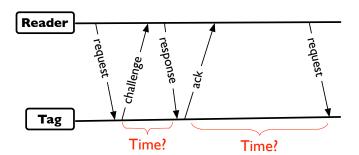

| 1.3    | The tag cannot determine the time between a challenge and a response or the time between two sessions. The reader could respond to the tag as tardily as it likes or query the tag as quickly as it wants                                                                                                                                                                                                                                   |

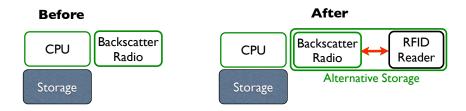

| 3.1    | CCCP exploits radio to offer a less energy-expensive alternative to local non-volatile storage. The main challenge of this work is to preserve the security and privacy of the tag-to-reader communication.                                                                                                                                                                                                                                 |

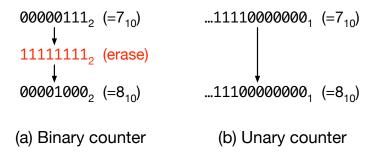

| 3.2    | Illustration of hole punching. While incrementing a binary counter (a) in flash memory may require an energy-intensive erase operation, complemented unary representation ((b), with the number of zeros, or "holes," representing the counter value) allows for incrementing without erasure at a cost of space efficiency                                                                                                                 |

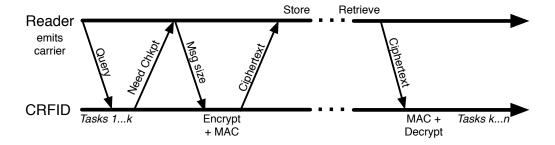

| 3.3 | Application-level view of the CCCP protocol. The CRFID sends a request to checkpoint state while in the presence of a reader, and the reader specifies the maximum size of each message. The CRFID then prepares the checkpoint and transmits it in a series of appropriately sized messages. The reader stores the checkpoint data for later retrieval by the CRFID. All messages from the reader to the CRFID also supply power to the CRFID if the latter is within range |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

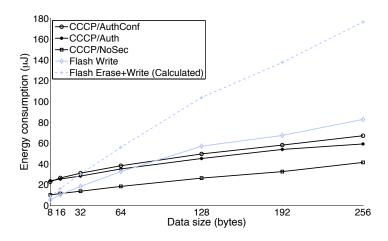

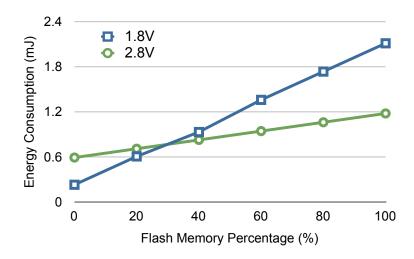

| 3.4 | Energy consumption measurements from a WISP (Revision 4.0) prototype for all considered checkpointing strategies. Under our experimental method, we are unable to execute flash writes larger than 256 bytes on current hardware because larger data sizes exhaust the maximum amount of energy available in a single energy lifecycle. The average and maximum percent error of the measurements are 5.85% and 14.08% respectively                                          |

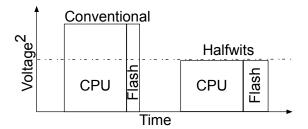

| 4.1 | Operating at a lower voltage and tolerating errors instead of the conventional case of choosing the highest minimum voltage requirement may help decrease energy consumption. Considering that $Energy = voltage^2 \times time/resistance$ , decreasing voltage decreases the energy consumption quadratically                                                                                                                                                               |

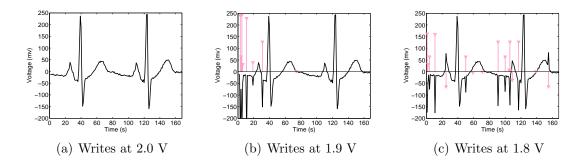

| 4.2 | As operating voltage decreases, flash-write errors increase. (a) shows an original ECG signal correctly stored at 2.0 V (despite operating below the recommended threshold). As the voltage decreases in (b) and further in (c), erroneous writes (light-colored spikes, height varying according to the magnitude of the error) become more common. The black line shows the reconstructed signal that includes the errors                                                  |

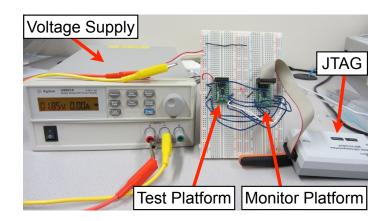

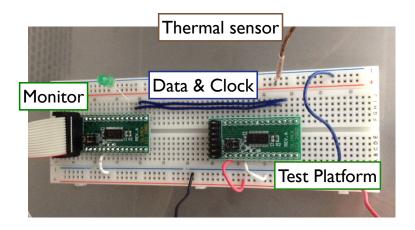

| 4.3 | Automated flash memory testbed. A monitoring platform observes and logs the behavior of the flash memory test platform. The test platform runs at a voltage controlled by the experimenter, while the monitoring platform runs at a constant voltage within the manufacturer's specified voltage. This setup helps to automate the experiments                                                                                                                               |

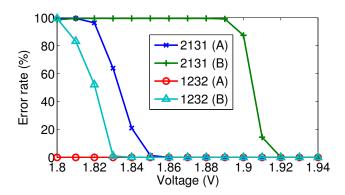

| 4.4 | Flash write error rates decrease as voltage increases. This trend holds for all the chips (MSP430F2131 and MSP430F1232) we tested, though error rates differ even between chips of the same model                                                                                                                                                                                                                                                                            |

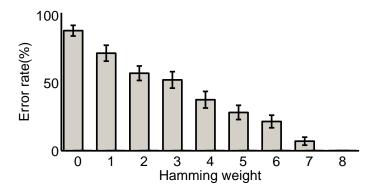

| 4.5  | As the Hamming weight (number of 1s in the binary representation) of a number increases, the error rate of low-voltage flash writes decline. The data correspond to a MSP430F2131 running at 1.84 V                                                                                                                                                                                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

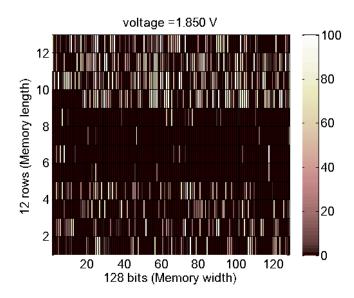

| 4.6  | Worn-out flash memory blocks are biased toward ease of writing zeros. Lighter color represents higher average number of errors over 50 trials. The middle block has been write/erase cycled 6,000 times. The other two blocks are minimally used                                                                                                                                                                                                                                                              |

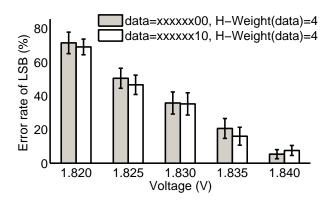

| 4.7  | Impact of the neighbor cells on error rate is negligible. The graph shows that the value of the second LSB does not greatly affect the error rate of the LSB. The bars show the error rate of the LSB for writing numbers from the same Hamming-weight equivalence class whose two LSBs are set to either 00 (dark bars) or to 10 (light bars)                                                                                                                                                                |

| 4.8  | Structure of the input/output sequence of the Berger code 62                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

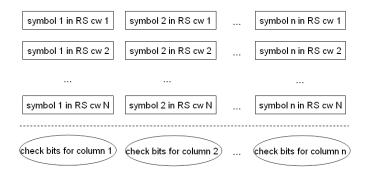

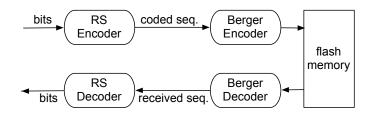

| 4.9  | A diagram representing the RS-Berger code. An RS-Berger code is the concatenation of the Reed Solomon code and a Berger code                                                                                                                                                                                                                                                                                                                                                                                  |

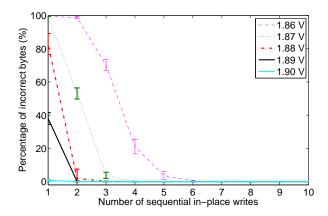

| 4.10 | Reliability improvement using <i>in-place writes</i> over five different voltages                                                                                                                                                                                                                                                                                                                                                                                                                             |

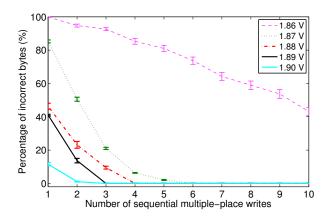

| 4.11 | Reliability improvement using multiple-place writes over five different voltages                                                                                                                                                                                                                                                                                                                                                                                                                              |

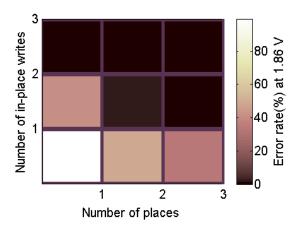

| 4.12 | The <i>in-place writes</i> method reduces the error rate more effectively than do the <i>multiple-place writes</i> method or a hybrid of both methods                                                                                                                                                                                                                                                                                                                                                         |

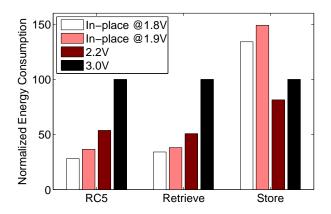

| 4.13 | Micro-benchmarks: CPU (RC5), read (retrieve), and write (store) normalized energy consumption measured at four different voltage levels. The energy has been normalized to the energy consumption of each workload at 3.0 V. Although the RC5 and retrieve test cases consume less energy at low voltage, this is not the case for the store test case (a write-intensive application) as the savings due to running the chip at low voltage do not compensate for the energy cost required to correct errors |

| 4.14 | Energy consumption of TI MSP430 microcontroller for different workloads of flash memory. The experimental results verify the calculation of finding the cross-over point at which <i>in-place writes</i> are competitive over normal flash writes. The cross-over point is where the time spent on computation is at least four times greater than the time spent on flash writes                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

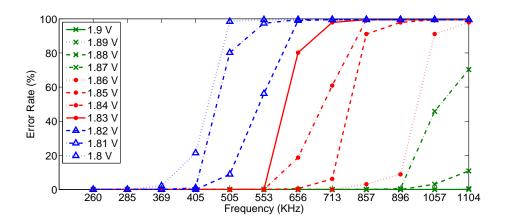

| 4.15 | Error rate declines when the writes are performed at a lower frequency. For a voltage level as low as 1.8 V, the average error rate becomes zero when the writes are performed at 260 KHz while for 1.9 V (still well below the recommended voltage), the average error rate is zero even if the memory is used at full speed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.16 | ECG data stored in flash memory at 1.89 V (the same chip from Figure 4.2) improved by using a sign bit. The light-colored bars show the difference between the ECG stored at low voltage and the original ECG data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

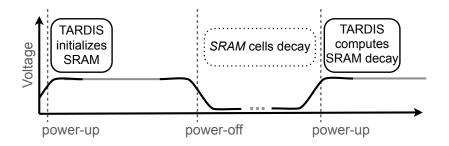

| 5.1  | TARDIS estimates time by counting the number of SRAM cells that have a value of zero in power-up (computes SRAM decay).  Initially, a portion of SRAM cells are set to one (initializes SRAM) and their values decay during power-off. The dots in the power-off indicate the arbitrary and unpredictable duration of power-off                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

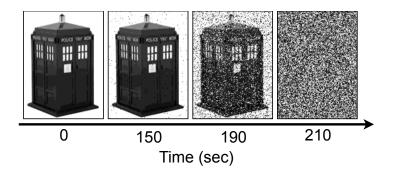

| 5.2  | Programs without access to a trustworthy clock can determine time elapsed during a power failure by observing the contents of uninitialized SRAM. These bitmap images of the TARDIS [1] represent four separate trials of storing the bitmap in SRAM, creating an open circuit across the voltage supply for the specified time at $26^{\circ}C$ , then immediately returning a normal voltage supply and reading uninitialized SRAM upon reboot. The architecture of a contactless card is modeled using a $10~\mu F$ capacitor and a diode in series with the MSP430 microcontroller's voltage supply pin. The degree of decay is a function of the duration of power failure, enabling hourglass-like timekeeping precision without power. No TARDIS was harmed or dematerialized in this experiment |

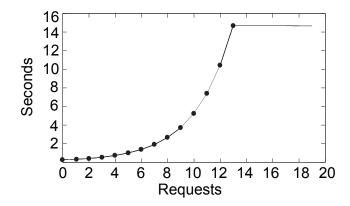

| 5.3  | Measured response time of a 2010-issued French passport [10]. The passport imposes up to 14 seconds of delay on its responses after unsuccessful execution. The delay will remain until a correct reading happens even if the passport were removed from the reader's field for a long time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

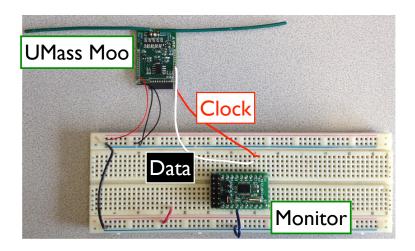

| 5.4 | Our applications are implemented and tested on the Moo RFID sensors and are remotely powered by a RFID reader (ThingMagic M5 [129])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

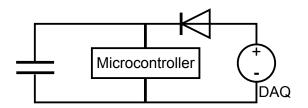

| 5.5 | General circuit used during the experiments. The microcontroller is held in an environmental chamber to ensure consistent temperature during the tests. The Data Acquisition (DAQ) unit both provides power to the microcontroller and records the voltage decay                                                                                                                                                                                                                                                                                                                                                               |

| 5.6 | The TARDIS presents a three-stage response pattern according to its amount of decay. Before 175 seconds, the percentage of bits that retain their 1-value across a power-off is 100%. For times exceeding 225 seconds, the TARDIS memory has fully decayed. The decay of memory cells between these two thresholds can provide us with a more accurate measurement of time during that period. This graph presents our results measured on a TI MSP430F2131 with 256 B of SRAM and a 10 $\mu F$ capacitor at $26^{\circ}C$ .                                                                                                   |

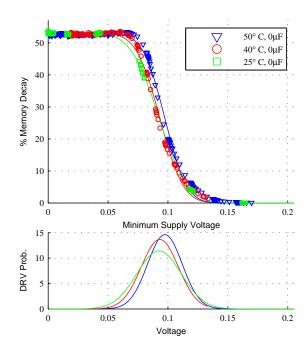

| 5.7 | Regardless of temperature, the amount of decay depends almost entirely on the minimum supply voltage reached during a power-down. The bottom graph shows the 3-parameter DRV probabilities (Equation A.3) that best predict the observed relationships between decay and minimum supply voltage for each of the three temperatures. The fit lines in the upper graph show the relationships between decay and minimum supply voltage that are predicted by these DRV models (Section A)                                                                                                                                        |

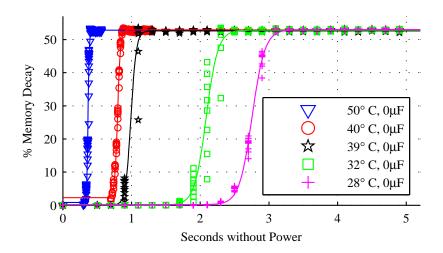

| 5.8 | The duration of SRAM decay is non-zero across all temperatures even when no capacitor is used. For any given temperature, the duration of SRAM decay is consistent across trials. Increasing the temperature from $28^{\circ}C$ to $50^{\circ}C$ reduces the duration of both Stage 1 and Stage 2 decay by approximately $80\%$                                                                                                                                                                                                                                                                                                |

| 5.9 | For five different capacitor values, measured supply voltage traces are combined with a pre-characterized DRV distribution to predict decay as a function of time. The decaying supply voltages after power is turned off are shown at left. The known DRV probabilities (Equation A.3) for $26.5^{\circ}C$ are shown at center. Equation A.4 maps every supply voltage measurement to a predicted decay, thus creating the memory-decay-vstime plots shown at right. The two horizontal lines in the left image at approximately 150 and 50 mV are the voltages where the first and last bits of SRAM will respectively decay |

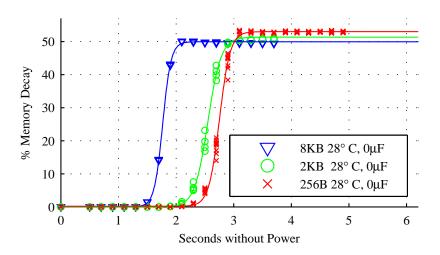

| 5.10 | SRAM sizes exhibit different decay times, but follow the same general trend. The MSP430F2618, MSP430F169, and MSP430F2131 respectively have 8 KB, 2 KB, and 256 B of SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

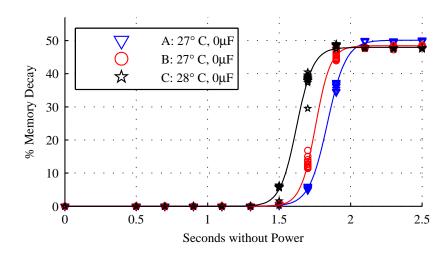

| 5.11 | Decay versus time in 3 different instances of the MSP430F2131 microcontroller at similar temperatures. The durations of Stage 1 and Stage 2 decay match closely across instances                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

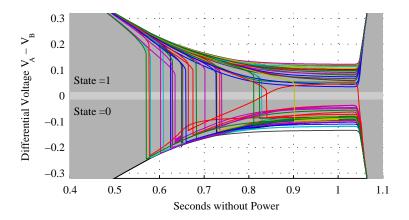

| 5.12 | The differential voltage of SRAM cells during decay. The envelope of $\pm V_{CC}$ is shaded in grey. All cells are in the 1 state when power is first turned off. As $V_{CC}$ decays, some cells flip from 1 to 0. The cells stabilize when power is restored. The number of zeros after the restoration of power is used to estimate the duration of the power outage                                                                                                                                                                                                                                                                |

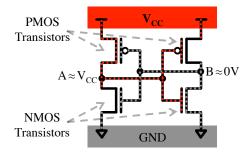

| 5.13 | The state-holding portion of an SRAM cell consists of two cross-coupled inverters tied to the chip's power and ground nodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

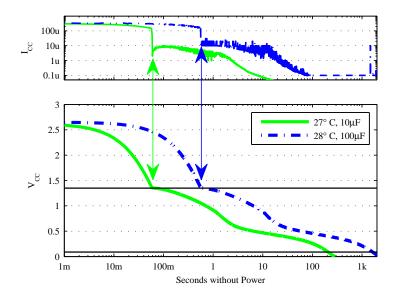

| 5.14 | Supply voltage and current during two power-down events with different capacitors. The voltage $V_{CC}$ is measured directly, and the current $I_{CC}$ is calculated per Equation 5.1 using the measured $\frac{dV_{CC}}{dt}$ and known capacitor values. The voltage initially decays rapidly due to the high current draw of the microcontroller. When $V_{CC}$ reaches 1.40V the microcontroller turns off and $I_{CC}$ drops by several orders of magnitude, leading to a long and slow voltage decay. At the time when $V_{CC}$ crosses the horizontal line at 0.09V, approximately half of all eligible cells will have decayed |

| 6.1  | Logging system for voltage measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.2  | Logging system for testing temperature. The whole system is tested inside a thermal chamber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

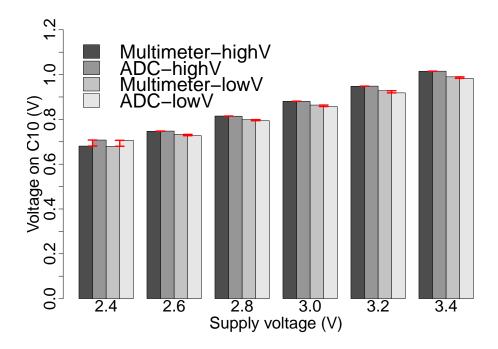

| 6.3  | Voltage measurements at low and high supply voltages using ADC and a multimeter. The mean of the error (the difference between the voltage measured using the ADC and the multimeter) is 1.30% and 0.71% for low (1.8 V) and high (>2.4 V) voltages respectively                                                                                                                                                                                                                                                                                                                                                                      |

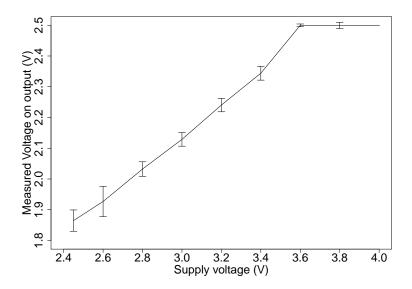

| 6.4 | Voltage measurement of the Vout using the ADC operating at 1.8 V.  The ADC cannot measure voltages greater than 2.5 V as the |

|-----|------------------------------------------------------------------------------------------------------------------------------|

|     | on-chip reference voltage generator cannot be set to anything higher than 2.5 V                                              |

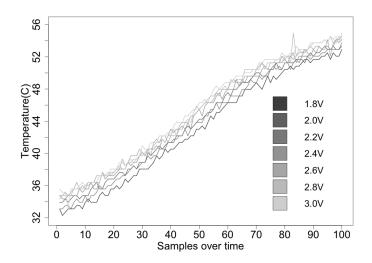

| 6.5 | Measured temperature at different operating voltages. The temperature has been raised from 30°C to 60°C                      |

| B.1 | Negin                                                                                                                        |

This page is intentionally left blank.

#### CHAPTER 1

#### INTRODUCTION

Recent years have witnessed a proliferation of low-power embedded devices [6, 22, 63, 75] with power ranges of few milliwatts (battery-powered) to microwatts (batteryless) [66]. The capabilities and size of the embedded systems continue to improve dramatically; however, improvements in battery density and energy harvesting have failed to mimic a Moore's law. The battery energy density is the slowest trend in mobile computing and it does not scale exponentially [93]. Thus, energy remains a formidable bottleneck for low-power embedded systems. For example, circuits of a smart lens can be miniaturized enough to be implanted inside an eye [56]; however, its corresponding batteries are not made small enough for such implantation.

#### 1.1 A Vision for a Cleaner World

Every year in United States alone, more than 3 billion batteries are purchased [4], a fraction of which is utilized to power embedded systems ranging from smoke detectors and utility meters to tollway payment transponders and pacemakers. I envision a future in which fewer chemical batteries are purchased and have landed on the earth even though the battery-operated devices continue to become computationally more powerful. Furthermore, batteryless devices are developed and utilized in places that have not been possible before.

Achieving this vision will require advances on many fronts: improvements in battery technologies in terms of energy per density, more productive energy harvesting schemes, better energy-aware programming languages, and new methods to reduce the energy consumption of existing devices. More fundamentally, we would like to redefine and reexamine design goals and requirements for low-power systems that are not as well equipped as their more powerful descendants, desktop computers.

#### 1.2 Thesis Overview

Rather than trying to create hardware with ideal energy proportionality, the thesis of this work is that we can use unconventional and probabilistic computing to bend traditional abstractions and interfaces in order to reduce energy consumption while protecting program semantics. In support of my thesis, I have designed and evaluated four software techniques that allow both battery-powered and batteryless devices to better exploit their power supplies: The first contribution, CCCP, exploits a passive radio to provide a less energy-hungry alternative to non-volatile storage. The primary challenge to this approach was to preserve data privacy and security. My other two contributions, Half-Wits and nonsensors, make energy consumption proportional to workload by operating the chip below safety margins while preserving data reliability. Finally, the TARDIS provides an hourglass-like timer which utilizes decay properties of volatile memory in an unconventional way to provide a secure notion of time. This timer is not as accurate as a clock but it requires no power to keep time. Table 1.1 summarizes the techniques and challenges to save energy for each of these four contributions.

| Contribution | Technique to Save Energy    | Research Challenge       |

|--------------|-----------------------------|--------------------------|

| CCCP         | Unconventional Use of Radio | Security & Privacy       |

| Half-Wits    | Probabilistic Storage       | Reliability              |

| TARDIS       | Unconventional Use of SRAM  | Security and Reliability |

| Nonsensors   | Probabilistic Sensing       | Reliability              |

**Table 1.1.** My thesis uses unconventional and probabilistic computing that bends traditional abstractions and interfaces in order to reduce energy consumption while protecting program semantics.

#### 1.3 CCCP, Secure Remote Storage for RFID Tags

Research involving low-energy computing systems has long treated radio as an energy-hungry resource to be used sparingly. This work, CCCP, exploits radio as a resource to amplify the storage capabilities of batteryless, programmable RFID tags. The main idea of this work is that a tag can securely use radio communication as a less energy-intensive alternative to local, flash-based storage. The smaller energy requirements of radio (Figure 1.1) allow the RFID tags either to devote more energy to computation or to accomplish the same tasks using less energy, which may translate into a longer operating range. CCCP uses established cryptographic mechanisms to protect against untrustworthy RFID readers that could attempt to violate the confidentiality, authenticity, integrity, and freshness of the data on a programable RFID tag. The main challenge in this work is to design an energy-saving remote storage system that provides security under the constraints of passive RFID systems. Our experiments show that—despite cryptographic overhead—remote checkpointing consumes less energy than checkpointing to flash for data sizes above roughly 64 bytes. CCCP enables secure and flexible remote storage that would otherwise outstrip batteryless RFID tags' resources. This work has been published in USENIX Security'09 [109].

**Figure 1.1.** Per-component maximum power consumption of two embedded devices. Radio communication on the WISP requires less power than writes to flash memory. The relative magnitudes of the power requirements means that a sensor mote favors shifting storage workloads to local flash memory instead of remote storage via radio, while a Computational RFID (CRFID) favors radio over flash.

#### 1.4 Half-Wits, Non-Volatile Storage at Low Voltage

While perfect data integrity is always an appealing target, system design constraints (e.g., energy scarcity) are likely to push systems towards execution modes in which less-than-perfect data integrity is sometimes tolerated, in exchange for improved power, density [86], or speed [15]. To enable energy-proportional computing for application-specific data, embedded storage systems ought to consider unconventional hardware-software interfaces that allow applications to provide reliability "hints" to hardware. This would allow the hardware to perform in a probabilistic manner that meets the application-level specifications without over-provisioning. The Half-Wits work shows how to reduce energy consumption by 30% by implementing NOR flash memory error recovery in firmware rather than strictly in hardware. The energy savings result from the ability to lower the supply voltage for components that share the same power rail with the flash memory. This research also indicates that significant energy savings are possible if application-specific data can tolerate bounded errors. This work has been published in USENIX FAST [110] and ACM TECS [111].

**Figure 1.2.** On a chip, different components have different minimum voltage requirements. Ideally, each component would have separate voltage sources and therefore the energy consumption of the device will be proportional to the workload. In practice, however, a chip has a single power source due to cost constraints. As a result, the energy consumption will be proportional to the worst case voltage requirement regardless of the workload.

#### 1.5 TARDIS, Secure Notion of Time for Batteryless Devices

Unawareness of time has left smart cards and RFID tags vulnerable to a number of successful attacks [91, 90, 20, 55]. A batteryless tag does not know about 1) the amount of time spent by the reader to answer the challenge and 2) the time between two different queries (Figure 1.3). A batteryless device could mitigate the risks of brute-force attacks, side-channel attacks, and reverse engineering by throttling its query response rate. However, the tag has no access to a trustworthy clock to implement throttling. The TARDIS keeps track of time by exploiting SRAM decay properties. In many ways, TARDIS operation resembles the functioning of an hourglass: the un-decayed, decaying, and fully decayed stages of SRAM are analogous to full, emptying, and empty hourglass states. Our experiments demonstrate that the TARDIS can measure time ranging from seconds to several hours depending on hardware parameters Key challenges to implementing a practical TARDIS include compensating for temperature and handling variation across hardware. This work has been published in USENIX Security [99].

**Figure 1.3.** The tag cannot determine the time between a challenge and a response or the time between two sessions. The reader could respond to the tag as tardily as it likes or query the tag as quickly as it wants.

#### 1.6 Nonsensors, Sensing at Low Voltage

Similar to the non-volatile storage, Analog to Digital Converters (ADCs) require relatively high voltage to guarantee functionality. For example, Texas Instruments MSP430F1232 requires the user to provide the ADC with at least 2.2 V to guarantee functionality while the CPU portion of the chip demands only 1.8 V. Table 1.2 shows more examples of popular microcontrollers with ADCs that restrict choices for the CPU voltage supply. This mismatch of voltage requirements causes energy disproportionality when the ADC and other on-board components share the same power rail. Nonsensors proposes to operate ADCs at the same voltage level as other embedded components to reduce the energy consumption of the whole system. To evaluate the nonsensors, we have designed a logging system that monitors and logs the output of ADC at low as well as high voltages. We define error as the measurement different of ADC at low and high voltage. Our preliminary results show that the ADC could work at voltages lower than specified by the chip manufacturers with introducing negligible errors (1.30%).

| Microcontroller                                 | CPU Minimum | ADC Minimum | Supply Voltage |

|-------------------------------------------------|-------------|-------------|----------------|

|                                                 | Voltage     | Voltage     | Gap            |

| TI MSP430F1232 [128] PIC32M [82] ATmega128L [9] | 1.8 V       | 2.2 V       | 22%            |

|                                                 | 2.5 V       | 3.0 V       | 20%            |

|                                                 | 2.7 V       | 4.5 V       | 66%            |

| STM32F103C6 [120]                               | 2.0 V       | 2.4 V       | 20%            |

**Table 1.2.** The ADC restricts choices for the CPU voltage supply on microcontrollers because the CPU shares the same power rail as the on-chip ADC.

#### 1.7 Summary of Contributions

To unleash energy otherwise squandered on storage, reliability, time keeping, or sensing, this thesis makes the following contributions:

- CCCP: A secure remote storage protocol that suits the characteristics and constraints of batteryless RFID tags, which can be used in the contexts of execution checkpointing and external data storage on an untrusted RFID reader infrastructure.

- 2. Half-Wits: A set of algorithms that enable reliable writes to flash memory while coping with low voltage, and an empirical evaluation that characterizes the behavior of on-chip flash memory at voltages below minimum levels specified by manufacturers.

- 3. TARDIS: Algorithmic building blocks to demonstrate the feasibility of using SRAM for a trustworthy source of time without power.

- 4. Nonsensors: Evaluation of operating analog to digital converters at low voltages without any hardware modifications to the existing circuitry.

This page is intentionally left blank.

#### CHAPTER 2

#### LOW-POWER EMBEDDED SYSTEMS

The focus of this thesis is on low-power devices with scarce energy resources; whether it is battery or it is harvested energy stored in capacitors. This chapter will give a brief background on battery-powered embedded systems and intermittently powered devices—batteryless devices that lose power regularly (e.g., passive RFID tags). Table 2.1 shows the abbreviations used in this thesis.

#### 2.1 Battery-powered Embedded Systems

Billions of embedded systems ranging from thermostats and utility meters to more recently-developed sensor motes run on batteries and having a small energy budget makes energy efficiency a top priority for them. There are many new energy-saving techniques developed for low-power embedded systems recently. For example, Blaauw et al. [15] reduce power consumption by lowering the operating voltage of a pipelined CPU. Certain pipeline stages may produce incorrect computation that require recomputation, but the errors can be made rare to allow better scalability of power consumption. In another case, Sorber et al. [118] introduced Eon, an energy-aware language and runtime system that measured energy harvesting and consumption. Eon automatically adjusts the device behavior as the energy conditions change.

However, not all embedded systems are taking full advantage of their energy resources. Most systems inherit algorithms from their powerful ancestors without much tailoring or tuning based on their limited resources. For example, most cryptography algorithms are designed and developed to perfection based on the assumption that

| Abbreviation | Full Name                                        |

|--------------|--------------------------------------------------|

| ADC          | Analog to Digital Conversion                     |

| CCCP         | Cryptographic Computational Continuation Passing |

| CPU          | Central Processing Unit                          |

| CRFID        | Computational RFID                               |

| DRV          | Data Retention Voltage                           |

| ECC          | Error Correction Code                            |

| ECG          | Electrocardiography                              |

| EPC          | Electronic Product Code                          |

| GPIO         | General Purpose Input/Output                     |

| RFID         | Radio Frequency IDentification                   |

| SRAM         | Static Random Access Memory                      |

| TARDIS       | Time And Remanence Decay In SRAM                 |

| TI           | Texas Instruments                                |

Table 2.1. Terminology

resources (memory, power, or time) available to the device are plenty. The choice of using RC5 [105] as is in a sensor mote [67] could be replaced with encryption algorithms that are designed with limited resources in mind [18].

Matching energy resources and energy demands remains a challenge for many battery-powered systems. Pacemakers and Implantable Cardiac Defibrillators often contain high-capacity lithium-based batteries that last five to seven years [133] which requires surgery for battery (device) replacement. Many home electronic devices such as smoke detectors and other sensing devices that use microcontrollers need battery maintenance very often. Wireless peripherals and game controllers have battery lifetime of months and hours respectively. The short lifetime of everyday electronic devices states the importance of improving energy efficiency of embedded system.

#### 2.2 Intermittently Powered Systems

Unlike battery-powered devices that assume their energy resource will be available on orders of months, batteryless system that live on harvested energy expect energy interruptions every few seconds. We define intermittently powered devices as systems that do not rely on constant source of power and faces reboots very regularly. Examples of devices targeted and experimented within this thesis are RFID tags and smart cards, both of which rely on Radio Frequency (RF) power.

#### 2.2.1 Computational RFID Tags

Consistent with the usage of RFID terminology, the term Computational RFID (CRFID) has two meanings: the model under which passively powered computers operate in concert with an RFID reader infrastructure, and the passively powered computers themselves. CRFIDs represent a class of programmable, batteryless computers [22, 101]. The small size and low maintenance requirements of CRFIDs make them especially appealing for adding computational capabilities to contexts in which placing or maintaining a conventional computer would be infeasible or impossible. However, CRFID systems require that nearby, actively powered RFID readers provide energy whenever computation is to occur, a requirement that may not suit all applications.

The components of a CRFID are: a low-power microcontroller; onboard RAM; flash memory (on or off the microcontroller); energy harvesting circuitry tuned to a certain frequency (e.g., 913 MHz for EPC Gen 2 RFID); an antenna; a transistor between the antenna and the microcontroller to modulate the antenna's impedance; a capacitor for storage of harvested energy; one or more analog-to-digital converters; and optional sensors for physical phenomena such as acceleration, heat, or light. The first working example of a CRFID is the Wireless Identification and Sensing Platform, or WISP [112], a prototype device slightly smaller than a postage stamp (discounting its inches-long antenna). The WISP is built around an off-the-shelf TI MSP430 microcontroller. Another example of a CRFID is UMass Moo [140], with a more powerful microcontroller, with additional memory, more pins for controlling sensors and actuators, and redesigned voltage regulation circuitry.

#### 2.2.2 Smart Cards

Smart cards which are also known as Integrated Circuit Cards (ICCs) refer to card-sized devices that contain an integrated circuit. Based on the way smart cards are powered up, they are considered contact or contactless. Contact smart cards which are more common than contactless ones, use six pins to communicate the a card reader. One of the pins is the VCC which should be in contact with the power pin of the reader. The contactless cards, harvest RF energy using their antenna and do not need to directly be in contact with the reader.

Although some smart cards are battery-powered, here we are talking about the ones that rely only on energy received from the reader. For example, contactless credit cards or transit cards are batteryless. The read time of card which is the equal to the power-up time is required to be less than 300ms–500ms (acceptable delay by customers to use a card). The short periods of power-up time makes smart cards count as intermittently-powered devices.

In addition to energy issues, the security and privacy of smart cards are usually challenging. Some RFID credit cards are vulnerable to replay attacks because they lack a notion of time [55]. Oswald et al. [91] recently demonstrated how to extract the 112-bit key from a MIFARE DESFire contactless smartcard (used by the Clipper all-in-one transit payment card). The side channel attack required approximately 10 queries/s for 7 hours. An earlier MIFARE classic chip was broken in 2008 by Nohl et a. [87]. Protecting the security and privacy of batteryless smart cards remains a challenging problem as long as there is no secure notion of time provided to smart cards.

#### CHAPTER 3

#### CCCP: SECURE REMOTE STORAGE FOR COMPUTATIONAL RFID TAGS

Passive RFID tags harvest their operating energy from an interrogating reader, but constant energy shortfalls severely limit their computational and storage capabilities. In this chapter, I propose *Cryptographic Computational Continuation Passing* (CCCP), a mechanism that amplifies programmable passive RFID tags' capabilities by exploiting an often overlooked, plentiful resource: low-power radio communication. While radio communication is more energy intensive than flash memory writes in many embedded devices, we show that the reverse is true for passive RFID tags.

The main idea of this work is that a CRFID can securely use radio communication as a less energy-intensive alternative to local, flash-based storage. The smaller energy requirements of radio allow the CRFID either to devote more energy to computation or to accomplish the same tasks using less energy, which may translate into a longer operating range.

**Figure 3.1.** CCCP exploits radio to offer a less energy-expensive alternative to local non-volatile storage. The main challenge of this work is to preserve the security and privacy of the tag-to-reader communication.

Security is the major challenge in such remote storage system. Using scant and fleeting energy, a tag must enforce confidentiality, authenticity, integrity, and data freshness while communicating with potentially untrustworthy infrastructure. This work contribution synthesizes well-known cryptographic and low-power techniques with a novel flash memory storage strategy, resulting in a secure remote storage facility for an emerging class of devices.

Evaluation of CCCP consists of energy measurements of a prototype implementation on the batteryless, MSP430-based Intel WISP platform. Experiments show that—despite cryptographic overhead—remote checkpointing consumes less energy than checkpointing to flash for data sizes above roughly 64 bytes. CCCP enables secure and flexible remote storage that would otherwise outstrip batteryless RFID tags' resources.

### 3.1 Frequent Power Loss on Tags, but Plentiful External Resources

Several key observations motivate the development of secure remote storage for computational RFIDs.

Frequent loss of power may interrupt computation. The CRFID model posits computing devices that are primarily powered by RF energy harvesting, a mechanism that is naturally finicky because of its dependence on physical conditions. Any change to a CRFID's physical situation—such as its position or the introduction of an occluding body—may affect its ability to harvest energy. Existing systems that use RF harvesting typically counteract the effect of physical conditions by placing stringent requirements on use. For example, an RFID transit card reader presented with a card may behave in an undefined way unless the card is within 1 cm for at least 300 ms, parameters designed to ensure that the card's computation finishes while it is still near the reader. CRFID applications may preclude such a strategy: programs on general-purpose CRFIDs may not offer convenient execution time horizons, and communication distances may not be easily controlled. Without any guarantees of

energy availability, it may be unreasonable to mandate that programs running on CRFIDs complete within a single energy lifecycle. As an extension of the Mementos system [101], CCCP aims to address the problem of suspending and resuming computations to facilitate spreading work across multiple energy lifecycles.

Storing remotely may require less energy than storing locally. Some amount of onboard nonvolatile memory exists on a CRFID, so an obvious approach to suspension and resumption is simply to use this local memory for state storage. However, to implement nonvolatile storage, current microcontrollers use flash memory, which imports several undesirable properties. While reading from flash consumes energy comparable to reading from volatile RAM, the other two flash operations—writing and erasing—require orders of magnitude more energy per datum (Table 3.3). Our measurements of a CRFID prototype reveal that the energy consumption of storing a datum locally in flash can in fact exceed the energy consumption of transmitting the same datum via backscatter communication.

To illustrate the difference between flash and radio storage on a CRFID and to show how the relationship is different on a sensor mote, we offer Figure 1.1. The figure helps explain why designers of mote-based systems choose to minimize radio communication; similarly, it justifies our exploration of radio-based storage as an alternative to flash-based storage on CRFIDs.

It should be noted that CCCP, although its primary data storage mechanism is the communication link between CRFIDs and readers, still requires *some* flash writes during storage operations: CCCP maintains a counter in flash to ensure that key material is not reused. However, because CCCP employs hole punching (Section 3.2.4.4) to maintain the counter, the amount of data written for counter updates is small compared to the amount of data that can be stored at once—small enough not to obviate the energy advantage of radio-based storage—and counter updates do not frequently necessitate erasures.

EPC Gen 2 RFID readers are typically not standalone devices. Rather, they are connected to networks or other systems (for, e.g., control or logging) that can offer computing resources such as storage. The benefit to CRFIDs that communicate with such a reader infrastructure is access to effectively limitless storage. Several kilobytes of onboard flash memory is minuscule compared to the potentially vast amount of storage available to networked RFID readers. While unlimited external storage is not obviously helpful for saving computational state—a CRFID cannot save or restore more state than it can hold locally—its usefulness as general-purpose long-term storage is analogous to the usefulness of networked storage for PCs.

RFID protocols allow arbitrary payloads. While the EPC Gen 2 protocol imposes constraints on the transmissions between RFID tags and RFID readers—for example, the maximum upstream data rate from tag to reader is 640 Kbps [37]—it also offers sufficient flexibility that CCCP can be implemented on top. In particular, the Gen 2 protocol permits a reader to issue a *Read* command to which a tag can respond with an arbitrary amount of data. Previous versions of the EPC RFID standard mandated a small response size that would have imposed severe communication overhead on large upstream transmissions.